AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

SPRS717H –OCTOBER 2011–REVISED MAY 2015

www.ti.com

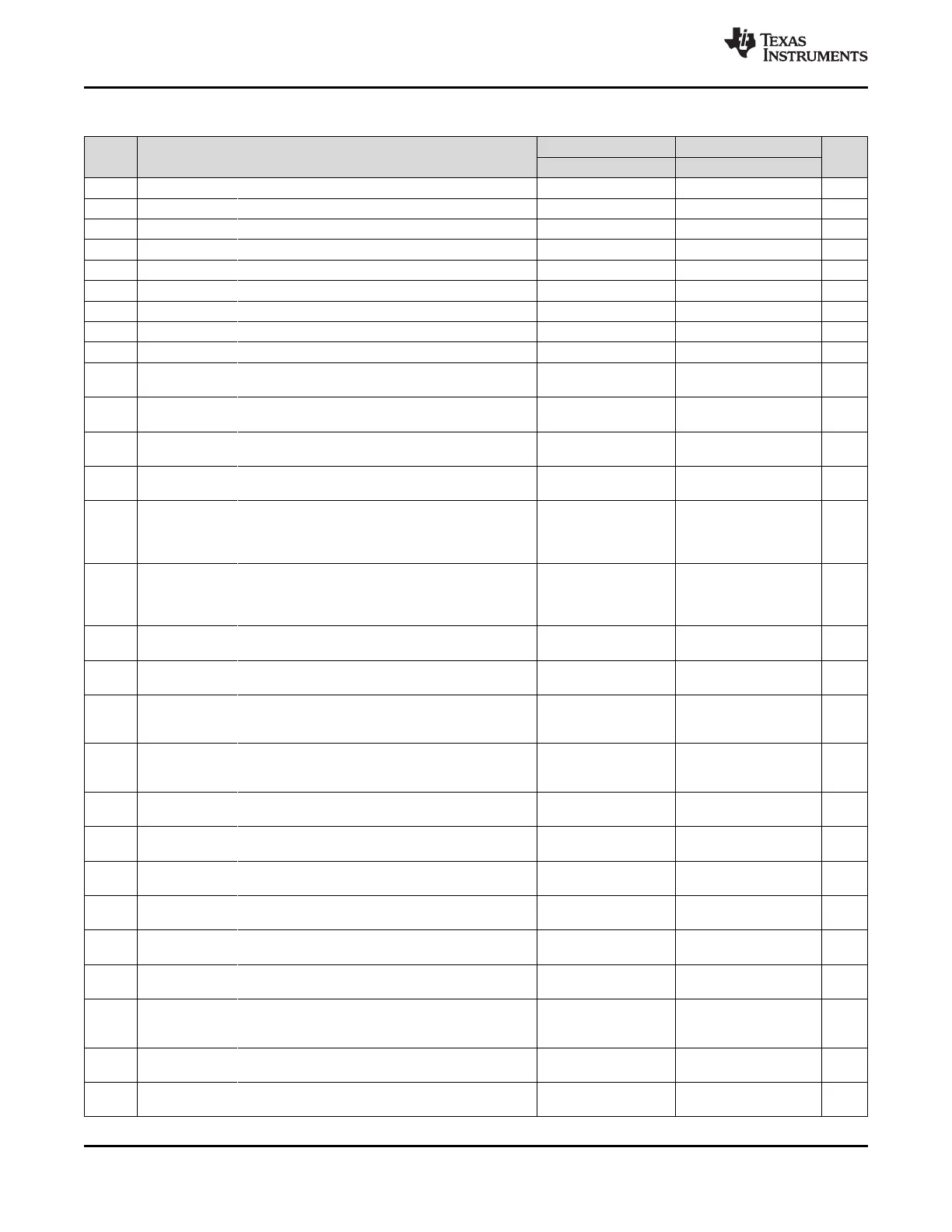

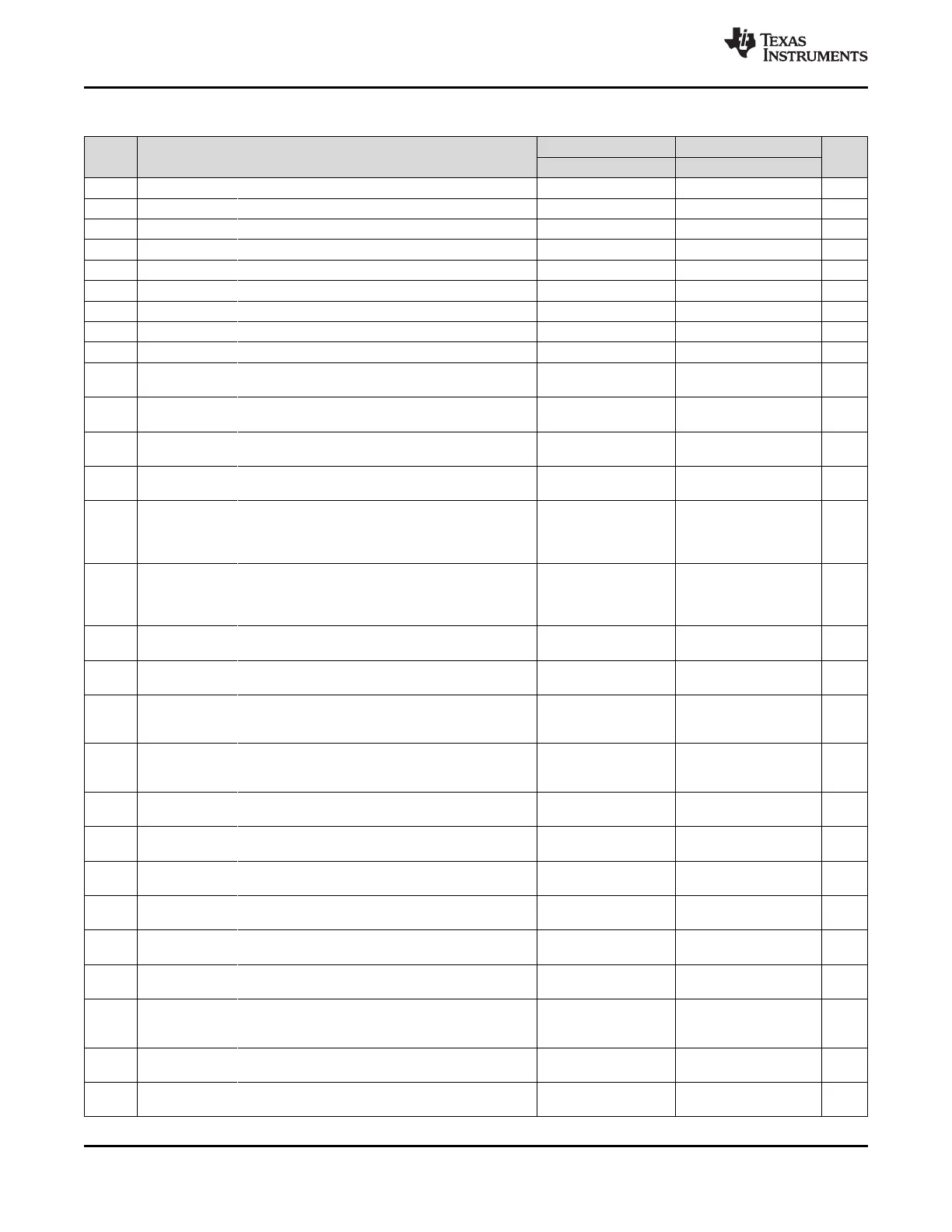

Table 7-22. GPMC and NOR Flash Switching Characteristics – Synchronous Mode

(2)

OPP100 OPP50

NO. PARAMETER UNIT

MIN MAX MIN MAX

F0 1 / t

c(clk)

Frequency

(18)

, output clock gpmc_clk 100 50 MHz

F1 t

w(clkH)

Typical pulse duration, output clock gpmc_clk high 0.5P

(15)

0.5P

(15)

0.5P

(15)

0.5P

(15)

ns

F1 t

w(clkL)

Typical pulse duration, output clock gpmc_clk low 0.5P

(15)

0.5P

(15)

0.5P

(15)

0.5P

(15)

ns

t

dc(clk)

Duty cycle error, output clock gpmc_clk –500 500 –500 500 ps

t

J(clk)

Jitter standard deviation

(19)

, output clock gpmc_clk 33.33 33.33 ps

t

R(clk)

Rise time, output clock gpmc_clk 2 2 ns

t

F(clk)

Fall time, output clock gpmc_clk 2 2 ns

t

R(do)

Rise time, output data gpmc_ad[15:0] 2 2 ns

t

F(do)

Fall time, output data gpmc_ad[15:0] 2 2 ns

F2 t

d(clkH-csnV)

Delay time, output clock gpmc_clk rising edge to F

(6)

- 2.2 F

(6)

+ 4.5 F

(6)

- 3.2 F

(6)

+ 9.5 ns

output chip select gpmc_csn[x]

(14)

transition

F3 t

d(clkH-csnIV)

Delay time, output clock gpmc_clk rising edge to E

(5)

– 2.2 E

(5)

+ 4.5 E

(5)

– 3.2 E

(5)

+ 9.5 ns

output chip select gpmc_csn[x]

(14)

invalid

F4 t

d(aV-clk)

Delay time, output address gpmc_a[27:1] valid to B

(2)

– 4.5 B

(2)

+ 2.3 B

(2)

– 5.5 B

(2)

+ 12.3 ns

output clock gpmc_clk first edge

F5 t

d(clkH-aIV)

Delay time, output clock gpmc_clk rising edge to –2.3 4.5 –3.3 14.5 ns

output address gpmc_a[27:1] invalid

F6 t

d(be[x]nV-clk)

Delay time, output lower byte enable and command B

(2)

– 1.9 B

(2)

+ 2.3 B

(2)

– 2.9 B

(2)

+ 12.3 ns

latch enable gpmc_be0n_cle, output upper byte

enable gpmc_be1n valid to output clock gpmc_clk

first edge

F7 t

d(clkH-be[x]nIV)

Delay time, output clock gpmc_clk rising edge to D

(4)

– 2.3 D

(4)

+ 1.9 D

(4)

– 3.3 D

(4)

+ 6.9 ns

output lower byte enable and command latch enable

gpmc_be0n_cle, output upper byte enable

gpmc_be1n invalid

(11)

F7 t

d(clkL-be[x]nIV)

Delay time, gpmc_clk falling edge to D

(4)

– 2.3 D

(4)

+ 1.9 D

(4)

– 3.3 D

(4)

+ 6.9 ns

gpmc_nbe0_cle, gpmc_nbe1 invalid

(12)

F7 t

d(clkL-be[x]nIV)

Delay time, gpmc_clk falling edge to D

(4)

– 2.3 D

(4)

+ 1.9 D

(4)

– 3.3 D

(4)

+ 11.9 ns

gpmc_nbe0_cle, gpmc_nbe1 invalid

(13)

F8 t

d(clkH-advn)

Delay time, output clock gpmc_clk rising edge to G

(7)

– 2.3 G

(7)

+ 4.5 G

(7)

– 3.3 G

(7)

+ 9.5 ns

output address valid and address latch enable

gpmc_advn_ale transition

F9 t

d(clkH-advnIV)

Delay time, output clock gpmc_clk rising edge to D

(4)

– 2.3 D

(4)

+ 3.5 D

(4)

– 3.3 D

(4)

+ 9.5 ns

output address valid and address latch enable

gpmc_advn_ale invalid

F10 t

d(clkH-oen)

Delay time, output clock gpmc_clk rising edge to H

(8)

– 2.3 H

(8)

+ 3.5 H

(8)

– 3.3 H

(8)

+ 8.5 ns

output enable gpmc_oen transition

F11 t

d(clkH-oenIV)

Delay time, output clock gpmc_clk rising edge to E

(8)

– 2.3 E

(8)

+ 3.5 E

(8)

– 3.3 E

(8)

+ 8.5 ns

output enable gpmc_oen invalid

F14 t

d(clkH-wen)

Delay time, output clock gpmc_clk rising edge to I

(9)

– 2.3 I

(9)

+ 4.5 I

(9)

– 3.3 I

(9)

+ 9.5 ns

output write enable gpmc_wen transition

F15 t

d(clkH-do)

Delay time, output clock gpmc_clk rising edge to J

(10)

– 2.3 J

(10)

+ 1.9 J

(10)

– 3.3 J

(10)

+ 6.9 ns

output data gpmc_ad[15:0] transition

(11)

F15 t

d(clkL-do)

Delay time, gpmc_clk falling edge to gpmc_ad[15:0] J

(10)

– 2.3 J

(10)

+ 1.9 J

(10)

– 3.3 J

(10)

+ 6.9 ns

data bus transition

(12)

F15 t

d(clkL-do)

Delay time, gpmc_clk falling edge to gpmc_ad[15:0] J

(10)

– 2.3 J

(10)

+ 1.9 J

(10)

– 3.3 J

(10)

+ 11.9 ns

data bus transition

(13)

F17 t

d(clkH-be[x]n)

Delay time, output clock gpmc_clk rising edge to J

(10)

– 2.3 J

(10)

+ 1.9 J

(10)

– 3.3 J

(10)

+ 6.9 ns

output lower byte enable and command latch enable

gpmc_be0n_cle transition

(11)

F17 t

d(clkL-be[x]n)

Delay time, gpmc_clk falling edge to J

(10)

– 2.3 J

(10)

+ 1.9 J

(10)

– 3.3 J

(10)

+ 6.9 ns

gpmc_nbe0_cle, gpmc_nbe1 transition

(12)

F17 t

d(clkL-be[x]n)

Delay time, gpmc_clk falling edge to J

(10)

– 2.3 J

(10)

+ 1.9 J

(10)

– 3.3 J

(10)

+ 11.9 ns

gpmc_nbe0_cle, gpmc_nbe1 transition

(13)

128 Peripheral Information and Timings Copyright © 2011–2015, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...