AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

www.ti.com

SPRS717H –OCTOBER 2011–REVISED MAY 2015

7.12 Multichannel Serial Port Interface (McSPI)

For more information, see the Multichannel Serial Port Interface (McSPI) section of the AM335x Sitara

Processors Technical Reference Manual (SPRUH73).

7.12.1 McSPI Electrical Data and Timing

The following timings are applicable to the different configurations of McSPI in master or slave mode for

any McSPI and any channel (n).

7.12.1.1 McSPI—Slave Mode

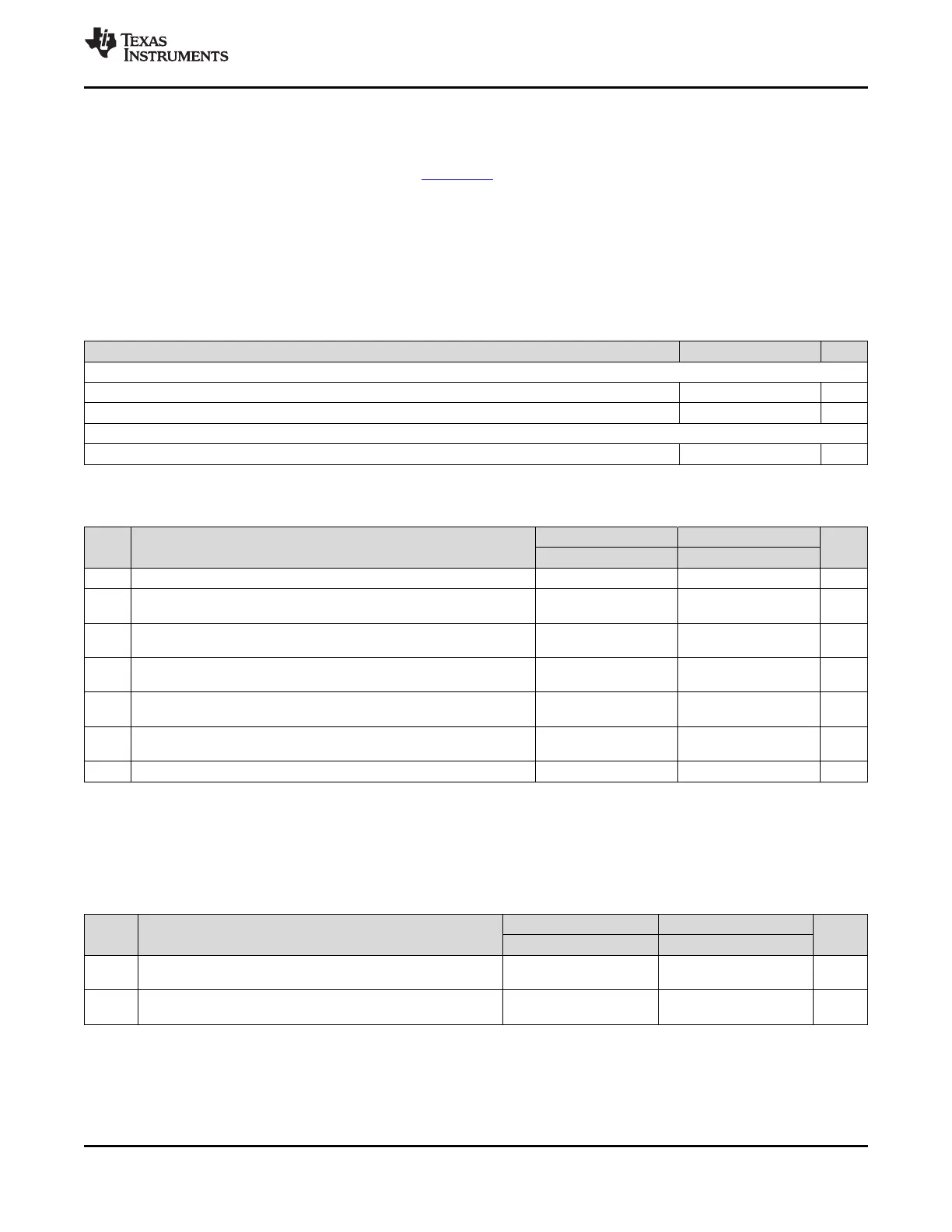

Table 7-80. McSPI Timing Conditions – Slave Mode

PARAMETER MIN MAX UNIT

Input Conditions

t

r

Input signal rise time 5 ns

t

f

Input signal fall time 5 ns

Output Condition

C

load

Output load capacitance 20 pF

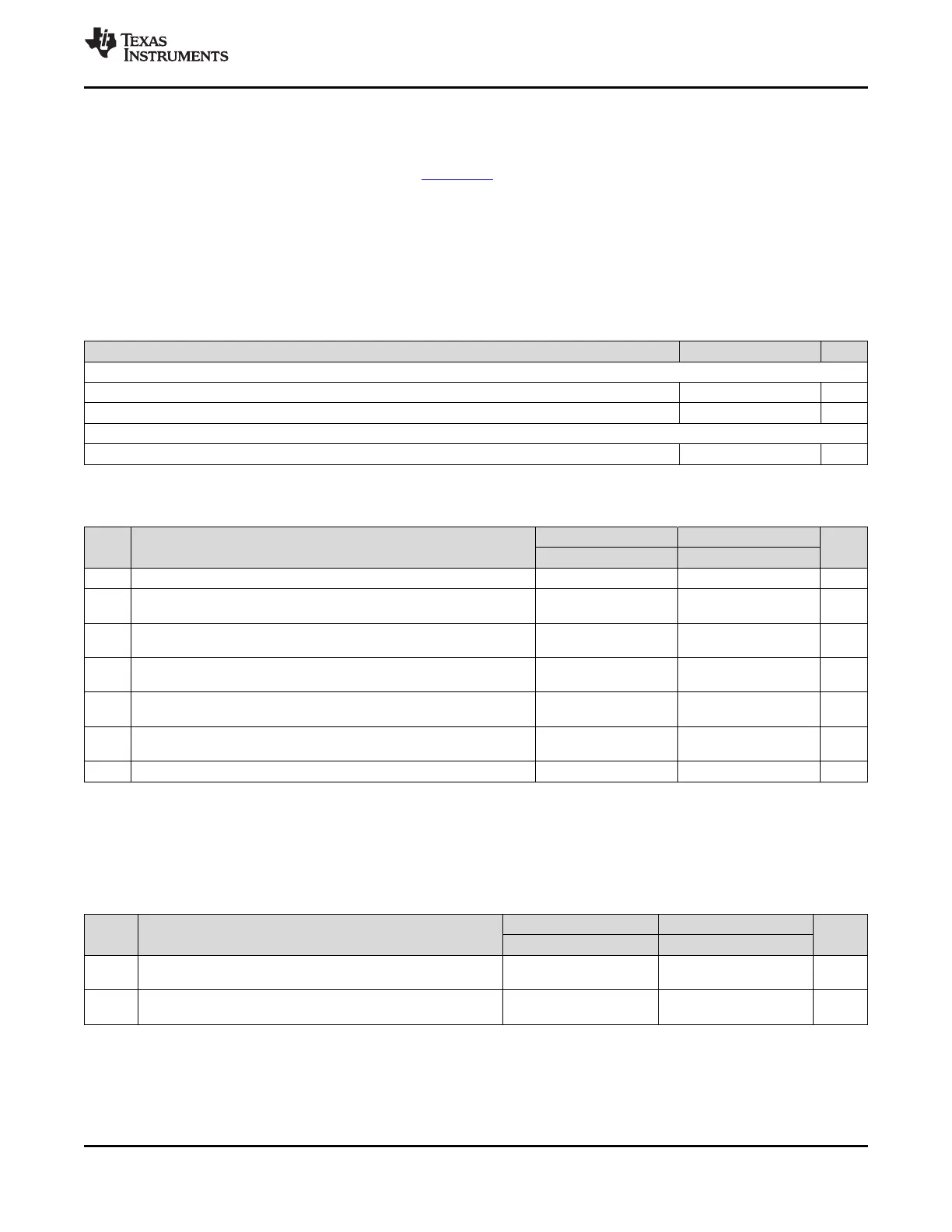

Table 7-81. Timing Requirements for McSPI Input Timings—Slave Mode

(see Figure 7-88)

OPP100 OPP50

NO. UNIT

MIN MAX MIN MAX

1 t

c(SPICLK)

Cycle time, SPI_CLK 62.5 124.8 ns

0.5P – 0.5P + 0.5P – 0.5P +

2 t

w(SPICLKL)

Typical pulse duration, SPI_CLK low ns

3.12

(1)

3.12

(1)

3.12

(1)

3.12

(1)

0.5P – 0.5P + 0.5P – 0.5P +

3 t

w(SPICLKH)

Typical pulse duration, SPI_CLK high ns

3.12

(1)

3.12

(1)

3.12

(1)

3.12

(1)

Setup time, SPI_D[x] (SIMO) valid before SPI_CLK

4 t

su(SIMO-SPICLK)

12.92 12.92 ns

active edge

(2)(3)

Hold time, SPI_D[x] (SIMO) valid after SPI_CLK

5 t

h(SPICLK-SIMO)

12.92 12.92 ns

active edge

(2)(3)

Setup time, SPI_CS valid before SPI_CLK first

8 t

su(CS-SPICLK)

12.92 12.92 ns

edge

(2)

9 t

h(SPICLK-CS)

Hold time, SPI_CS valid after SPI_CLK last edge

(2)

12.92 12.92 ns

(1) P = SPI_CLK period.

(2) This timing applies to all configurations regardless of MCSPIX_CLK polarity and which clock edges are used to drive output data and

capture input data.

(3) Pins SPIx_D0 and SPIx_D1 can function as SIMO or SOMI.

Table 7-82. Switching Characteristics for McSPI Output Timings—Slave Mode

(see Figure 7-89)

OPP100 OPP50

NO. PARAMETER UNIT

MIN MAX MIN MAX

Delay time, SPI_CLK active edge to

6 t

d(SPICLK-SOMI)

–4.00 17.12 –4.00 17.12 ns

SPI_D[x] (SOMI) transition

(1)(2)

Delay time, SPI_CS active edge to

7 t

d(CS-SOMI)

17.12 17.12 ns

SPI_D[x] (SOMI) transition

(1)(2)

(1) This timing applies to all configurations regardless of MCSPIX_CLK polarity and which clock edges are used to drive output data and

capture input data.

(2) Pins SPIx_D0 and SPIx_D1 can function as SIMO or SOMI.

Copyright © 2011–2015, Texas Instruments Incorporated Peripheral Information and Timings 215

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...