AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

www.ti.com

SPRS717H –OCTOBER 2011–REVISED MAY 2015

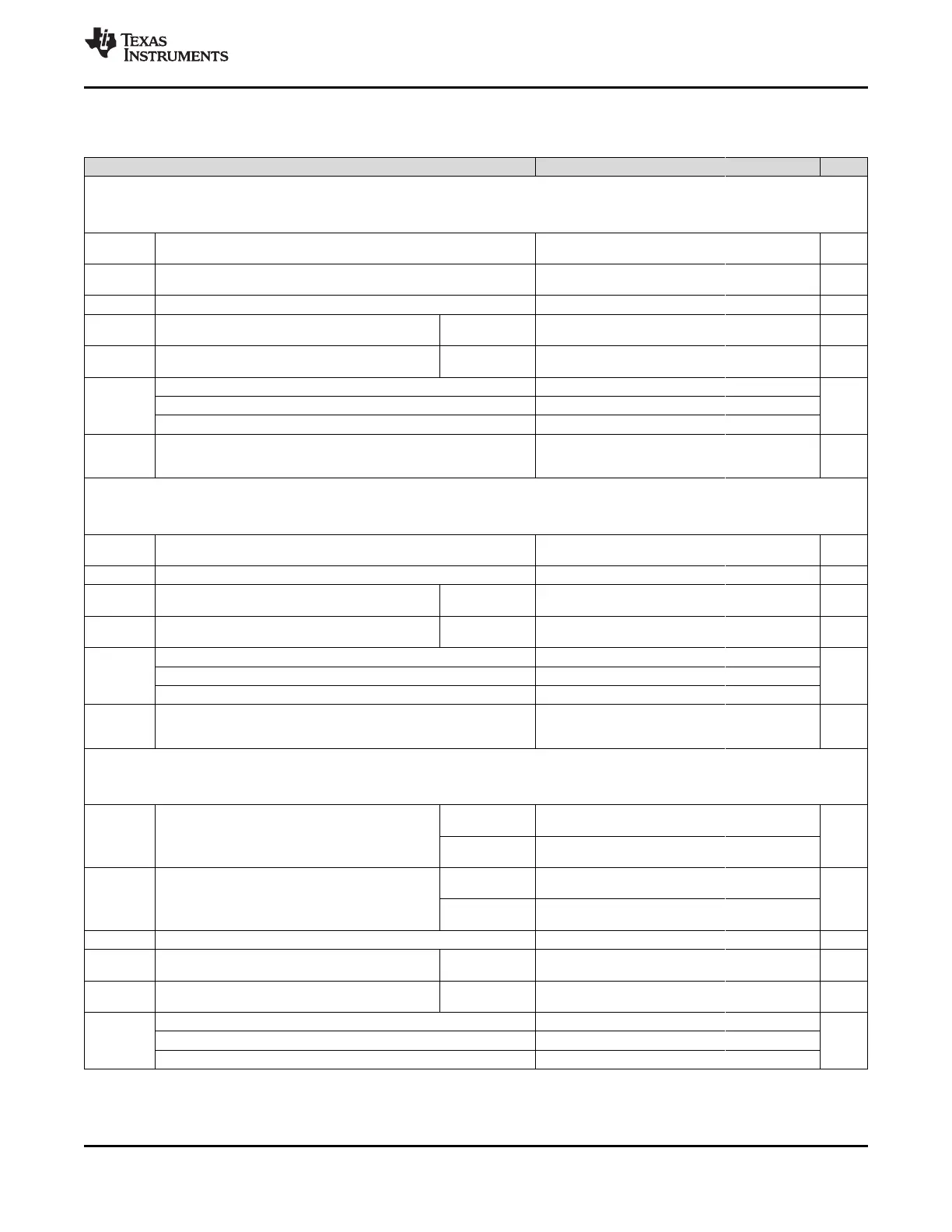

5.7 DC Electrical Characteristics

(1)

over recommended ranges of supply voltage and operating temperature (unless otherwise noted)

PARAMETER MIN NOM MAX UNIT

DDR_RESETn,DDR_CSn0,DDR_CKE,DDR_CK,DDR_CKn,DDR_CASn,DDR_RASn,DDR_WEn,DDR_BA0,DDR_BA1,DDR_BA2,DDR_A0,DDR_A1,DDR_A

2,DDR_A3,DDR_A4,DDR_A5,DDR_A6,DDR_A7,DDR_A8,DDR_A9,DDR_A10,DDR_A11,DDR_A12,DDR_A13,DDR_A14,DDR_A15,DDR_ODT,DDR_D0,DD

R_D1,DDR_D2,DDR_D3,DDR_D4,DDR_D5,DDR_D6,DDR_D7,DDR_D8,DDR_D9,DDR_D10,DDR_D11,DDR_D12,DDR_D13,DDR_D14,DDR_D15,DDR_DQM

0,DDR_DQM1,DDR_DQS0,DDR_DQSn0,DDR_DQS1,DDR_DQSn1 Pins (mDDR - LVCMOS Mode)

0.65 ×

V

IH

High-level input voltage V

VDDS_DDR

0.35 ×

V

IL

Low-level input voltage V

VDDS_DDR

V

HYS

Hysteresis voltage at an input 0.07 0.25 V

High level output voltage, driver enabled, pullup or VDDS_DDR –

V

OH

I

OH

= 8 mA V

pulldown disabled 0.4

Low level output voltage, driver enabled, pullup or

V

OL

I

OL

= 8 mA 0.4 V

pulldown disabled

Input leakage current, Receiver disabled, pullup or pulldown inhibited 10

I

I

Input leakage current, Receiver disabled, pullup enabled –240 –80 µA

Input leakage current, Receiver disabled, pulldown enabled 80 240

Total leakage current through the terminal connection of a driver-receiver

I

OZ

combination that may include a pullup or pulldown. The driver output is 10 µA

disabled and the pullup or pulldown is inhibited.

DDR_RESETn,DDR_CSn0,DDR_CKE,DDR_CK,DDR_CKn,DDR_CASn,DDR_RASn,DDR_WEn,DDR_BA0,DDR_BA1,DDR_BA2,DDR_A0,DDR_A1,DDR_A

2,DDR_A3,DDR_A4,DDR_A5,DDR_A6,DDR_A7,DDR_A8,DDR_A9,DDR_A10,DDR_A11,DDR_A12,DDR_A13,DDR_A14,DDR_A15,DDR_ODT,DDR_D0,DD

R_D1,DDR_D2,DDR_D3,DDR_D4,DDR_D5,DDR_D6,DDR_D7,DDR_D8,DDR_D9,DDR_D10,DDR_D11,DDR_D12,DDR_D13,DDR_D14,DDR_D15,DDR_DQM

0,DDR_DQM1,DDR_DQS0,DDR_DQSn0,DDR_DQS1,DDR_DQSn1 Pins (DDR2 - SSTL Mode)

V

IH

High-level input voltage DDR_VREF + V

0.125

V

HYS

Hysteresis voltage at an input N/A V

V

OH

High-level output voltage, driver enabled, pullup or I

OH

= 8 mA VDDS_DDR – V

pulldown disabled 0.4

V

OL

Low-level output voltage, driver enabled, pullup or I

OL

= 8 mA 0.4 V

pulldown disabled

Input leakage current, Receiver disabled, pullup or pulldown inhibited 10

I

I

Input leakage current, Receiver disabled, pullup enabled –240 –80 µA

Input leakage current, Receiver disabled, pulldown enabled 80 240

I

OZ

Total leakage current through the terminal connection of a driver-receiver 10 µA

combination that may include a pullup or pulldown. The driver output is

disabled and the pullup or pulldown is inhibited.

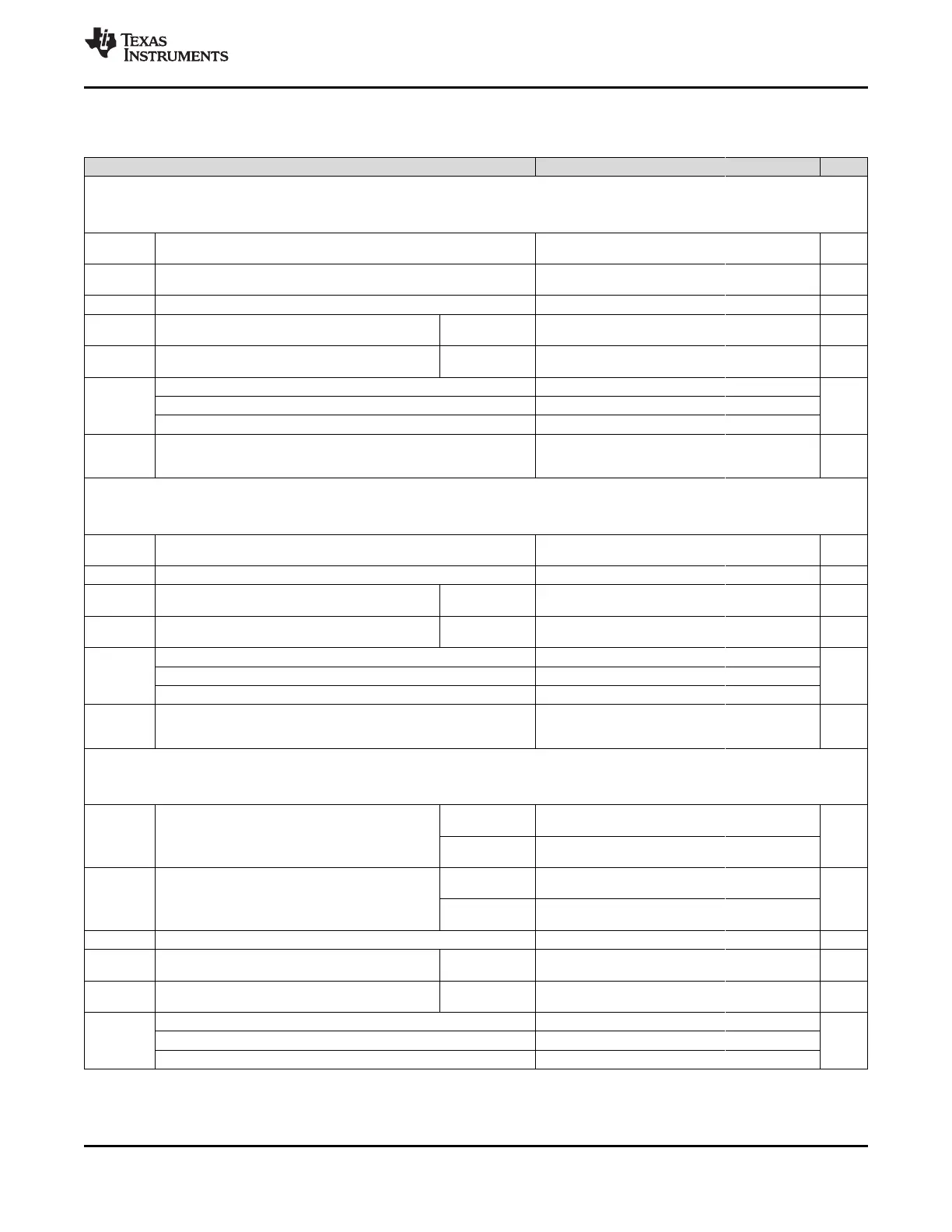

DDR_RESETn,DDR_CSn0,DDR_CKE,DDR_CK,DDR_CKn,DDR_CASn,DDR_RASn,DDR_WEn,DDR_BA0,DDR_BA1,DDR_BA2,DDR_A0,DDR_A1,DDR_A

2,DDR_A3,DDR_A4,DDR_A5,DDR_A6,DDR_A7,DDR_A8,DDR_A9,DDR_A10,DDR_A11,DDR_A12,DDR_A13,DDR_A14,DDR_A15,DDR_ODT,DDR_D0,DD

R_D1,DDR_D2,DDR_D3,DDR_D4,DDR_D5,DDR_D6,DDR_D7,DDR_D8,DDR_D9,DDR_D10,DDR_D11,DDR_D12,DDR_D13,DDR_D14,DDR_D15,DDR_DQM

0,DDR_DQM1,DDR_DQS0,DDR_DQSn0,DDR_DQS1,DDR_DQSn1 Pins (DDR3, DDR3L - HSTL Mode)

V

IH

High-level input voltage VDDS_DDR = DDR_VREF + V

1.5 V 0.1

VDDS_DDR = DDR_VREF +

1.35 V 0.09

VDDS_DDR = DDR_VREF –

1.5 V 0.1

V

IL

Low-level input voltage V

VDDS_DDR = DDR_VREF –

1.35 V 0.09

V

HYS

Hysteresis voltage at an input N/A V

V

OH

High-level output voltage, driver enabled, pullup or I

OH

= 8 mA VDDS_DDR – V

pulldown disabled 0.4

V

OL

Low-level output voltage, driver enabled, pullup or I

OL

= 8 mA 0.4 V

pulldown disabled

Input leakage current, Receiver disabled, pullup or pulldown inhibited 10

I

I

Input leakage current, Receiver disabled, pullup enabled –240 –80 µA

Input leakage current, Receiver disabled, pulldown enabled 80 240

(1) The interfaces or signals described in this table correspond to the interfaces or signals available in multiplexing mode 0. All interfaces or

signals multiplexed on the terminals described in this table have the same dc electrical characteristics.

Copyright © 2011–2015, Texas Instruments Incorporated Specifications 89

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...