AM3359, AM3358, AM3357, AM3356, AM3354, AM3352

www.ti.com

SPRS717H –OCTOBER 2011–REVISED MAY 2015

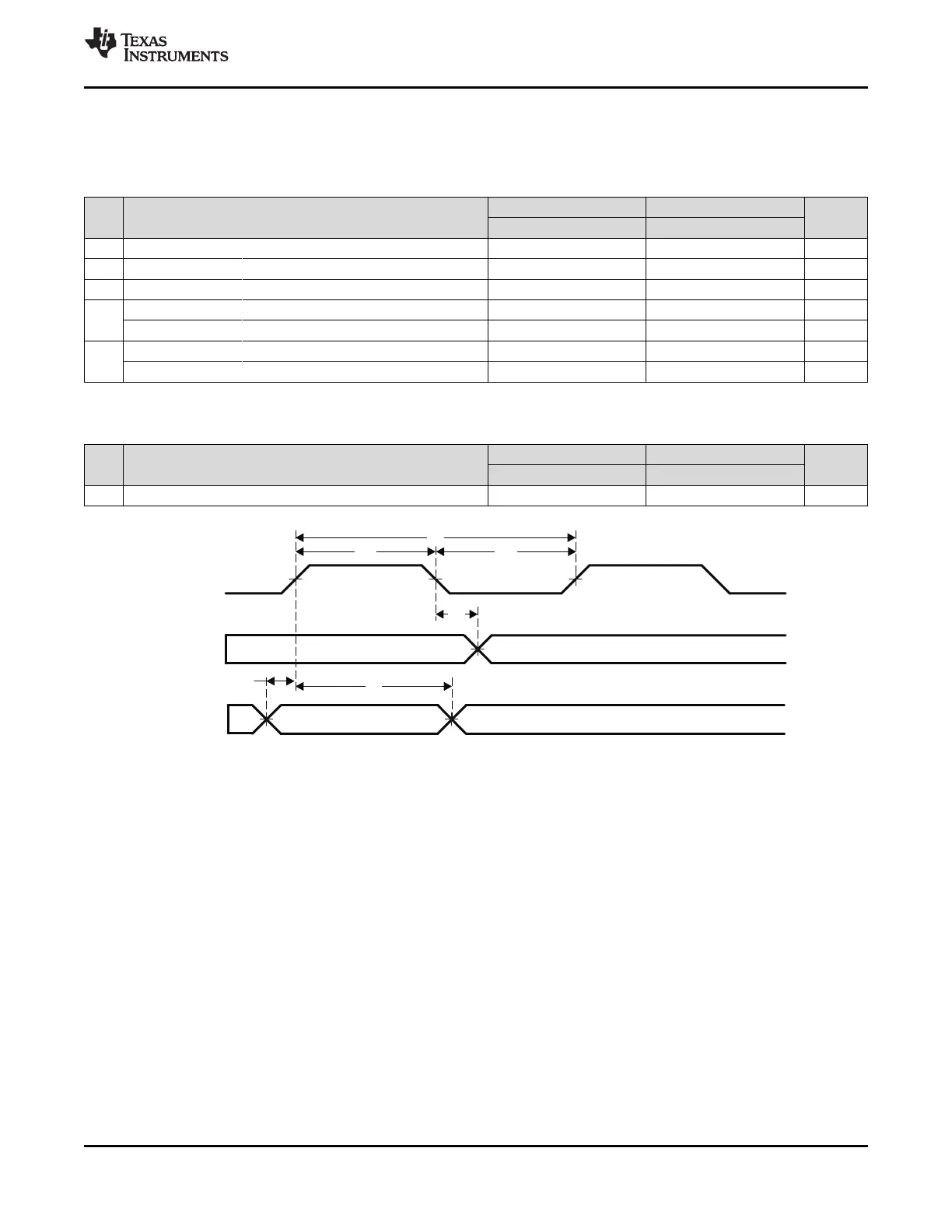

7.9 JTAG Electrical Data and Timing

Table 7-71. Timing Requirements for JTAG

(see Figure 7-70)

OPP100 OPP50

NO. UNIT

MIN MAX MIN MAX

1 t

c(TCK)

Cycle time, TCK 81.5 104.5 ns

1a t

w(TCKH)

Pulse duration, TCK high (40% of t

c

) 32.6 41.8 ns

1b t

w(TCKL)

Pulse duration, TCK low (40% of t

c

) 32.6 41.8 ns

t

su(TDI-TCKH)

Input setup time, TDI valid to TCK high 3 3 ns

3

t

su(TMS-TCKH)

Input setup time, TMS valid to TCK high 3 3 ns

t

h(TCKH-TDI)

Input hold time, TDI valid from TCK high 8.05 8.05 ns

4

t

h(TCKH-TMS)

Input hold time, TMS valid from TCK high 8.05 8.05 ns

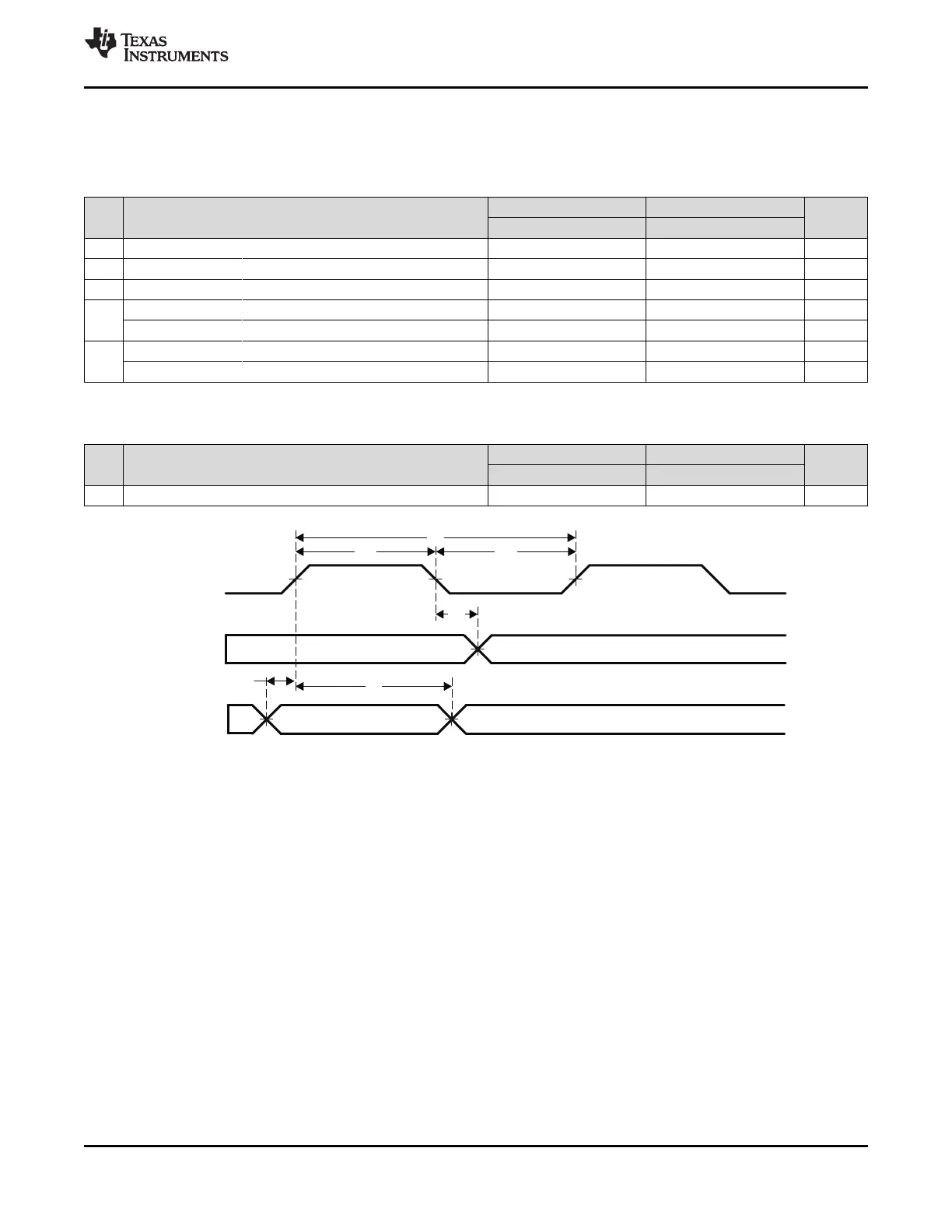

Table 7-72. Switching Characteristics for JTAG

(see Figure 7-70)

OPP100 OPP50

NO. PARAMETER UNIT

MIN MAX MIN MAX

2 t

d(TCKL-TDO)

Delay time, TCK low to TDO valid 3 27.6 4 36.8 ns

Figure 7-70. JTAG Timing

Copyright © 2011–2015, Texas Instruments Incorporated Peripheral Information and Timings 193

Submit Documentation Feedback

Product Folder Links: AM3359 AM3358 AM3357 AM3356 AM3354 AM3352

Loading...

Loading...