Overview of Thread Scheduling

4-10

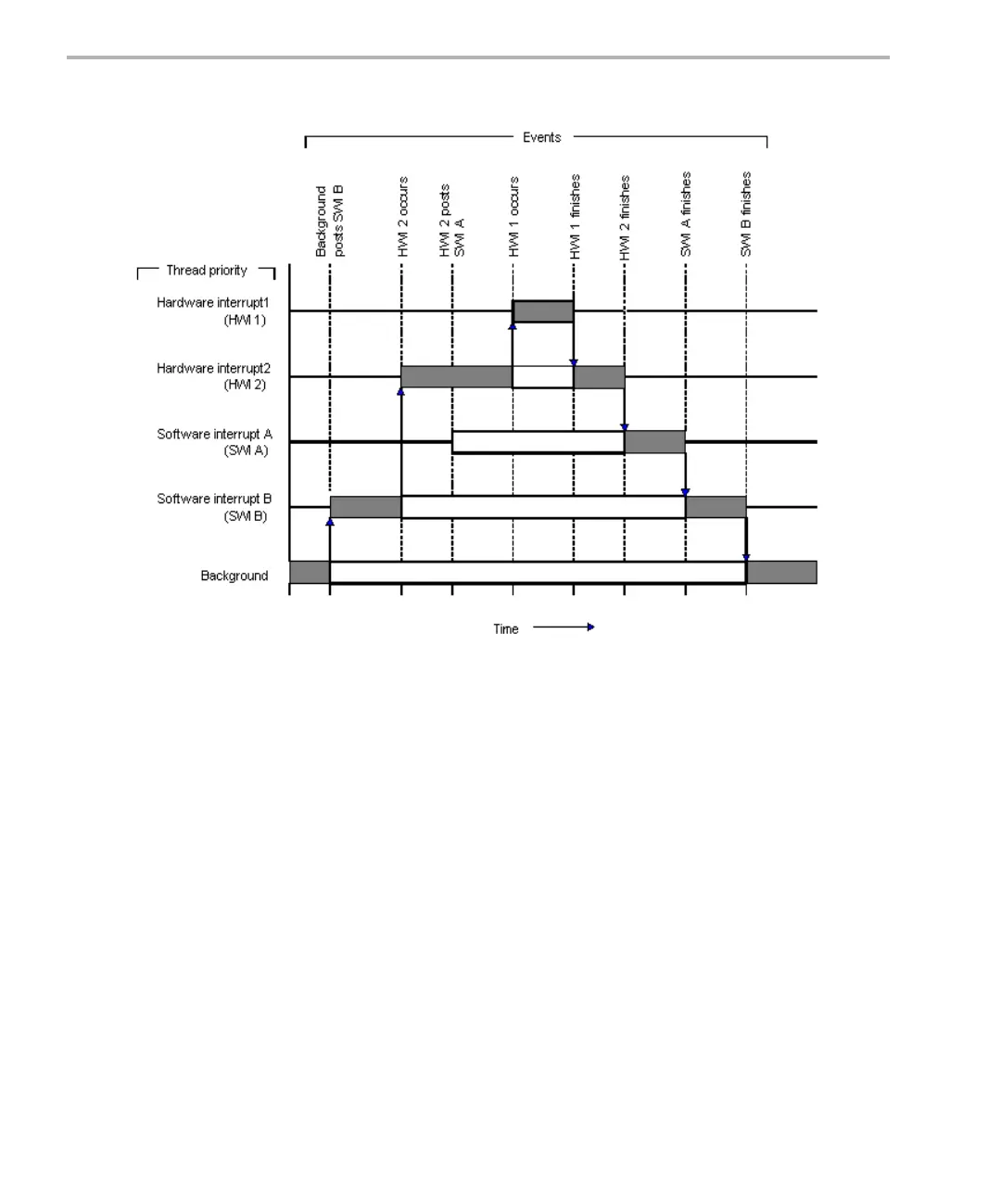

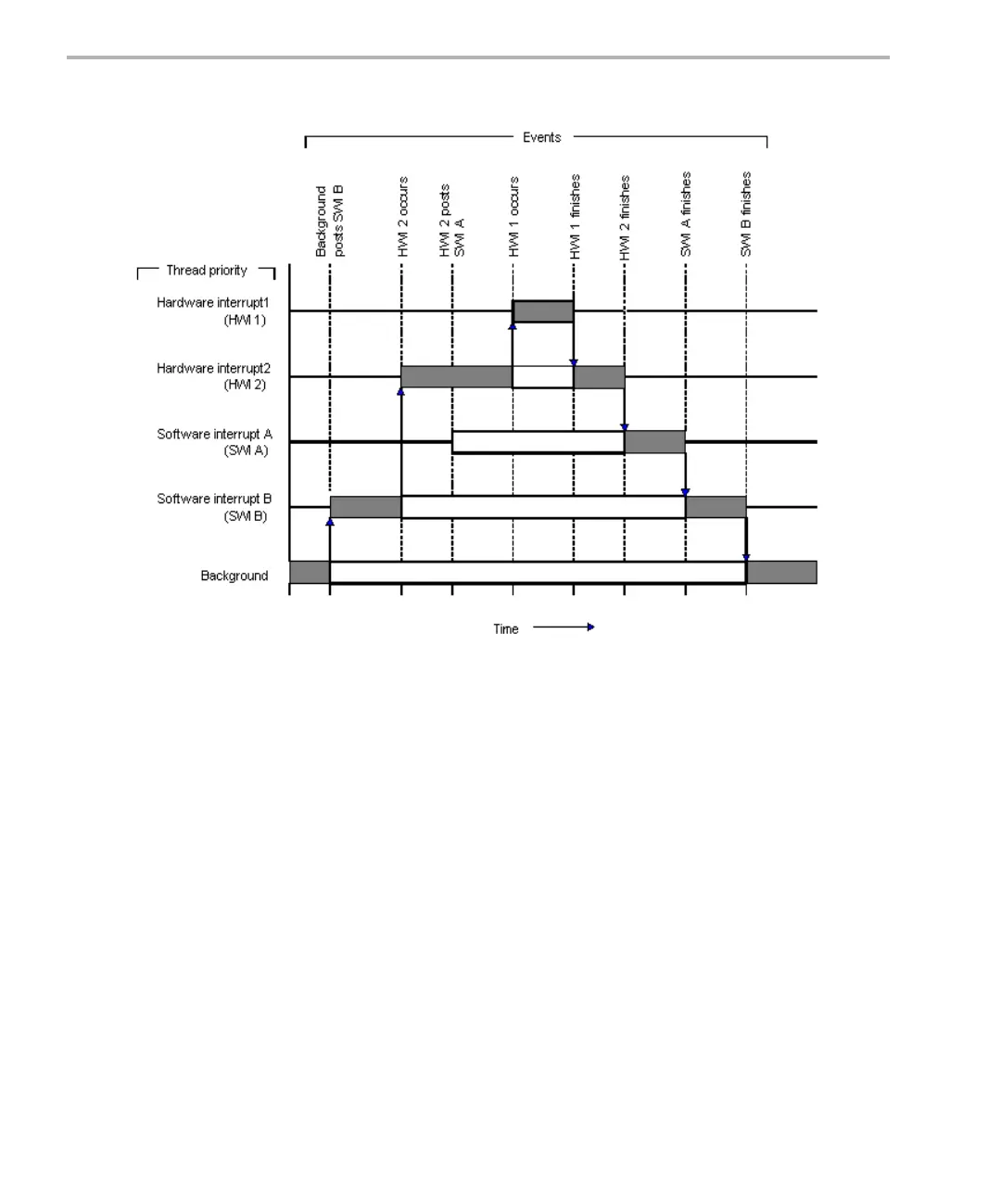

Figure 4-2. Preemption Scenario

In Figure 4-2, the low priority software interrupt is asynchronously preempted

by the hardware interrupts. The first ISR posts a higher-priority software

interrupt, which is executed after both hardware interrupt routines finish

executing.

Loading...

Loading...