125

TMS320F28069

,

TMS320F28068

,

TMS320F28067

,

TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com

SPRS698F –NOVEMBER 2010–REVISED MARCH 2016

Submit Documentation Feedback

Product Folder Links: TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

Detailed DescriptionCopyright © 2010–2016, Texas Instruments Incorporated

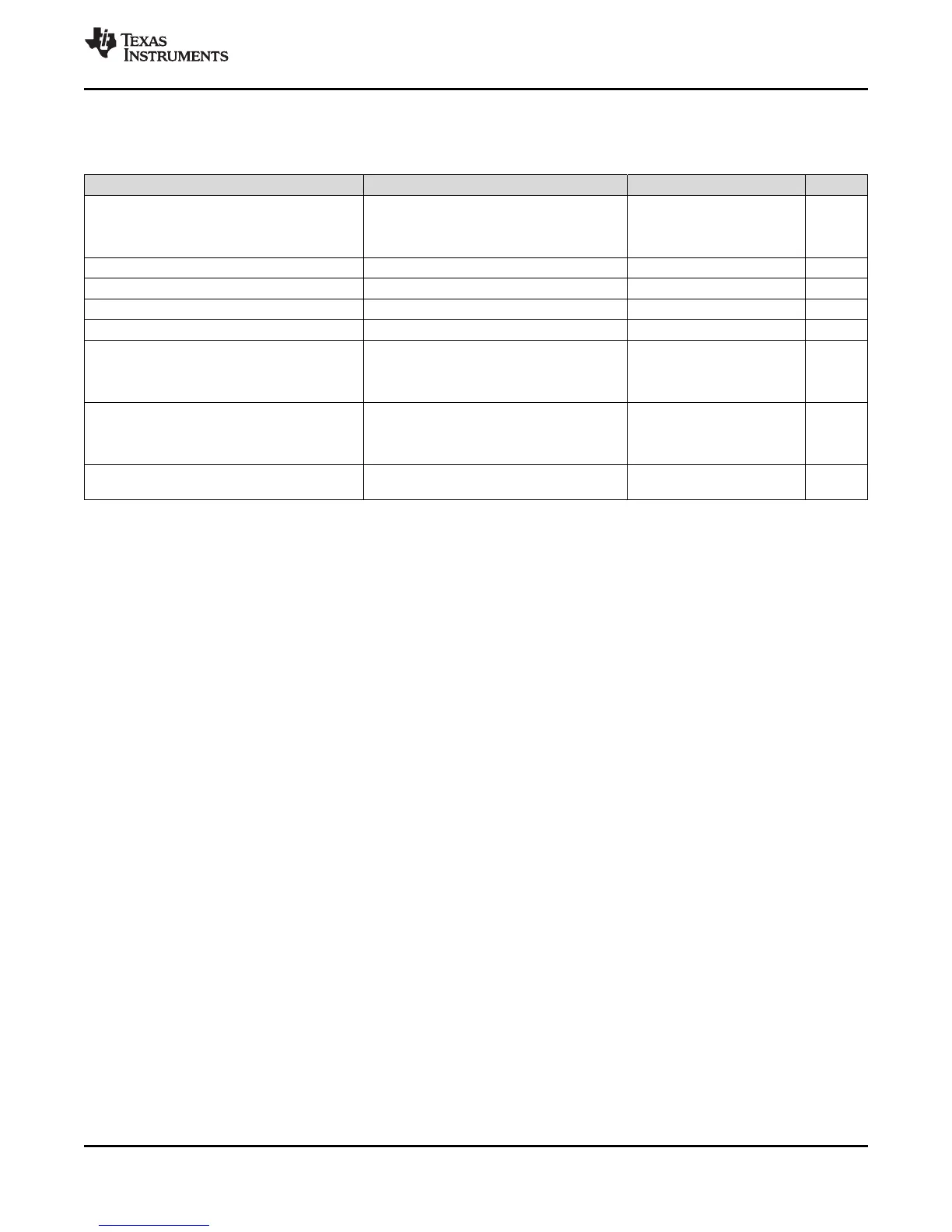

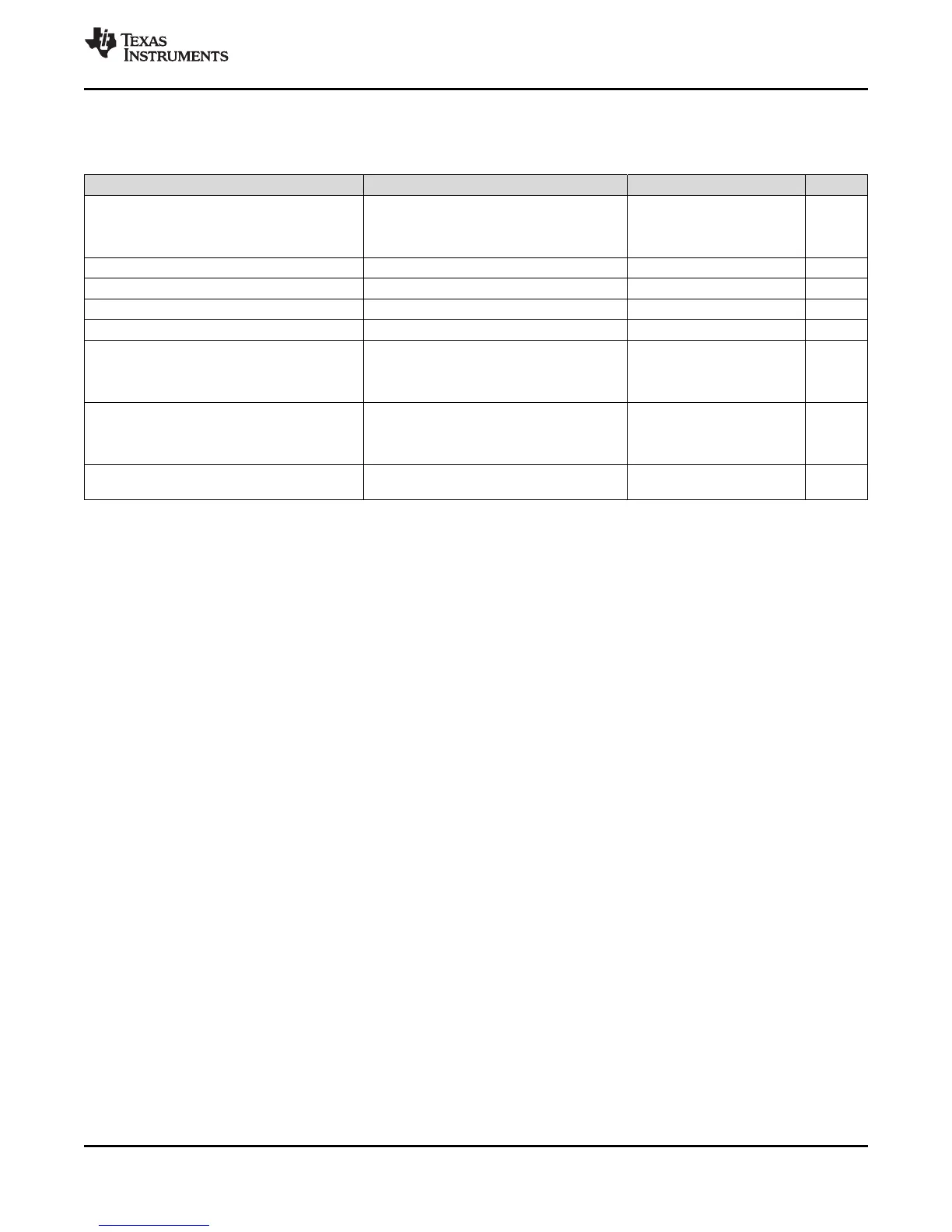

6.9.8.1 I

2

C Electrical Data/Timing

Table 6-55. I

2

C Timing

TEST CONDITIONS MIN MAX UNIT

f

SCL

SCL clock frequency

I

2

C clock module frequency is between

7 MHz and 12 MHz and I

2

C prescaler and

clock divider registers are configured

appropriately

400 kHz

v

il

Low level input voltage 0.3 V

DDIO

V

V

ih

High level input voltage 0.7 V

DDIO

V

V

hys

Input hysteresis 0.05 V

DDIO

V

V

ol

Low level output voltage 3-mA sink current 0 0.4 V

t

LOW

Low period of SCL clock

I

2

C clock module frequency is between

7 MHz and 12 MHz and I

2

C prescaler and

clock divider registers are configured

appropriately

1.3 μs

t

HIGH

High period of SCL clock

I

2

C clock module frequency is between

7 MHz and 12 MHz and I

2

C prescaler and

clock divider registers are configured

appropriately

0.6 μs

l

I

Input current with an input voltage

between 0.1 V

DDIO

and 0.9 V

DDIO

MAX

–10 10 μA

Loading...

Loading...