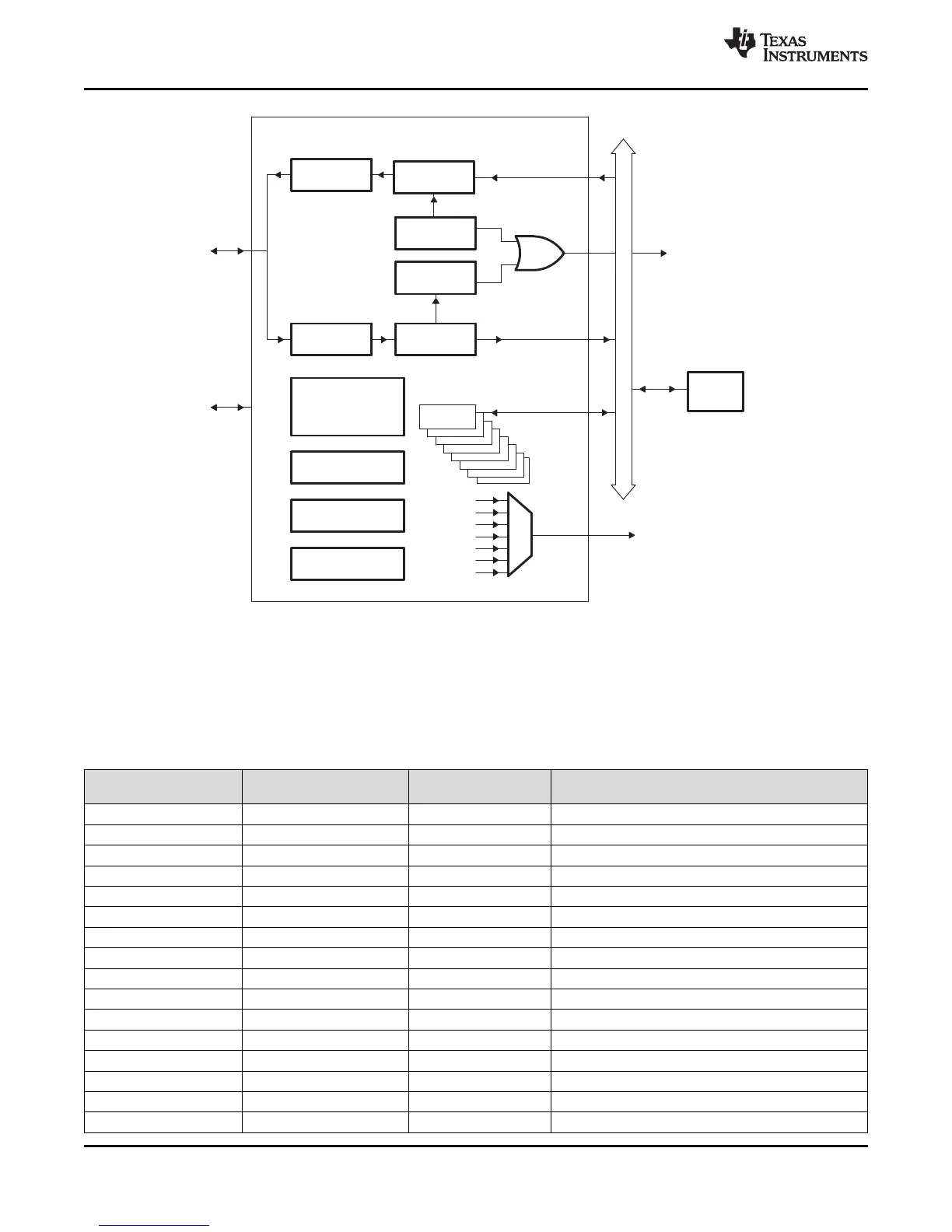

I2CXSR

I2CDXR

I2CRSR

I2CDRR

Clock

Synchronizer

Prescaler

Noise Filters

Arbitrator

I2C INT

Peripheral Bus

Interrupt to

CPU/PIE

SDA

SCL

Control/Status

Registers

CPU

I C Module

2

TX FIFO

RX FIFO

FIFO Interrupt to

CPU/PIE

124

TMS320F28069

,

TMS320F28068

,

TMS320F28067

,

TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

SPRS698F –NOVEMBER 2010–REVISED MARCH 2016

www.ti.com

Submit Documentation Feedback

Product Folder Links: TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

Detailed Description Copyright © 2010–2016, Texas Instruments Incorporated

A. The I

2

C registers are accessed at the SYSCLKOUT rate. The internal timing and signal waveforms of the I

2

C port are

also at the SYSCLKOUT rate.

B. The clock enable bit (I2CAENCLK) in the PCLKCRO register turns off the clock to the I

2

C port for low power

operation. Upon reset, I2CAENCLK is clear, which indicates the peripheral internal clocks are off.

Figure 6-47. I

2

C Peripheral Module Interfaces

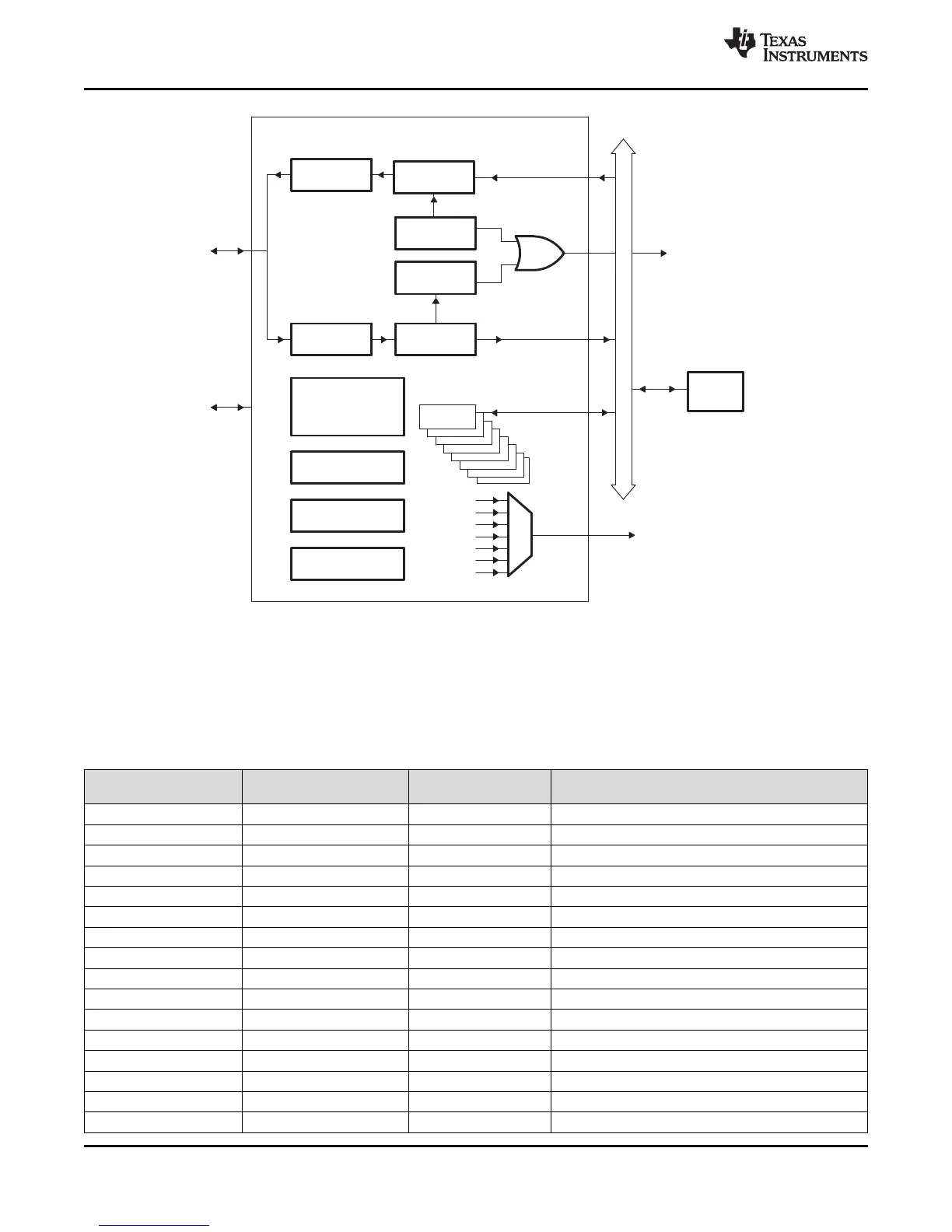

The registers in Table 6-54 configure and control the I

2

C port operation.

Table 6-54. I2C-A Registers

NAME ADDRESS

EALLOW

PROTECTED

DESCRIPTION

I2COAR 0x7900 No I

2

C own address register

I2CIER 0x7901 No I

2

C interrupt enable register

I2CSTR 0x7902 No I

2

C status register

I2CCLKL 0x7903 No I

2

C clock low-time divider register

I2CCLKH 0x7904 No I

2

C clock high-time divider register

I2CCNT 0x7905 No I

2

C data count register

I2CDRR 0x7906 No I

2

C data receive register

I2CSAR 0x7907 No I

2

C slave address register

I2CDXR 0x7908 No I

2

C data transmit register

I2CMDR 0x7909 No I

2

C mode register

I2CISRC 0x790A No I

2

C interrupt source register

I2CPSC 0x790C No I

2

C prescaler register

I2CFFTX 0x7920 No I

2

C FIFO transmit register

I2CFFRX 0x7921 No I

2

C FIFO receive register

I2CRSR – No I

2

C receive shift register (not accessible to the CPU)

I2CXSR – No I

2

C transmit shift register (not accessible to the CPU)

Loading...

Loading...