1. OUTLINE EO10-33016A

1.5 Electronics Specifications

1- 7

1.5 Electronics Specifications

1) CPU: HD6417705F133BV

2) Memory

(1) Program: 16-MB Flash ROM

(2) Backup: 512-byte EE-PROM

(3) Image buffer + Work: 16-MB SD-RAM

3) Interface

(1) Parallel interface (Standard interface)

c Centronics interface conforming to IEEE1284, supporting SPP mode (compatibility mode) and

nibble mode.

d Data input method: 8-bit parallel (DATA 1 to 8)

e Control signals

Compatibility mode

nStrobe, nAck, Busy, PError, Select, nAutoFd, nInit, nFault, nSelectIn

Nibble mode HostClk, PtrClk, PtrBusy, AckDataReq, Xflag, HostBusy, nInit, nDataAvail,

IEEE1284Active

f Data input code: ASCII, JIS 8-bit code for European characters, 8-bit code for graphic

g Receiving buffer: 1MB (shared with other interfaces)

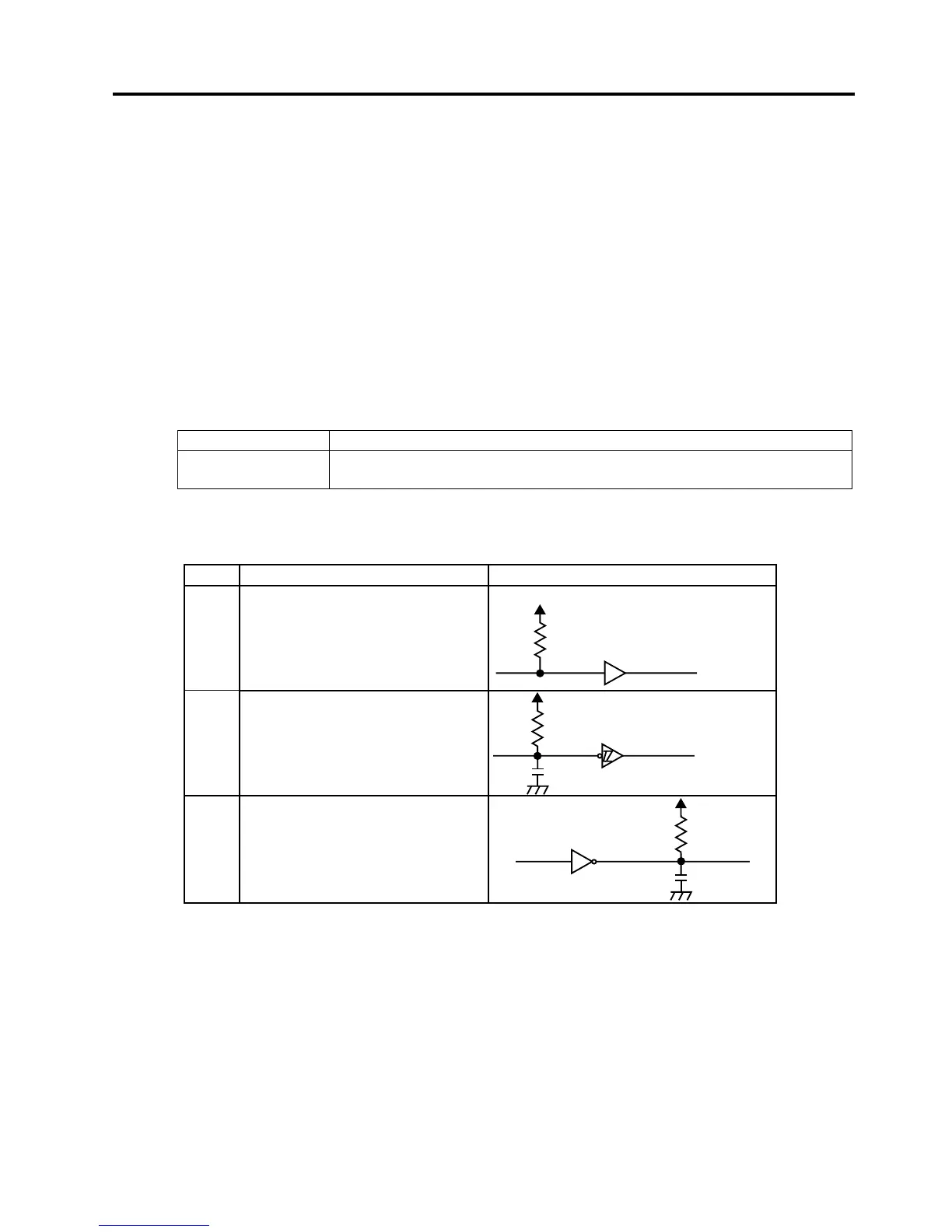

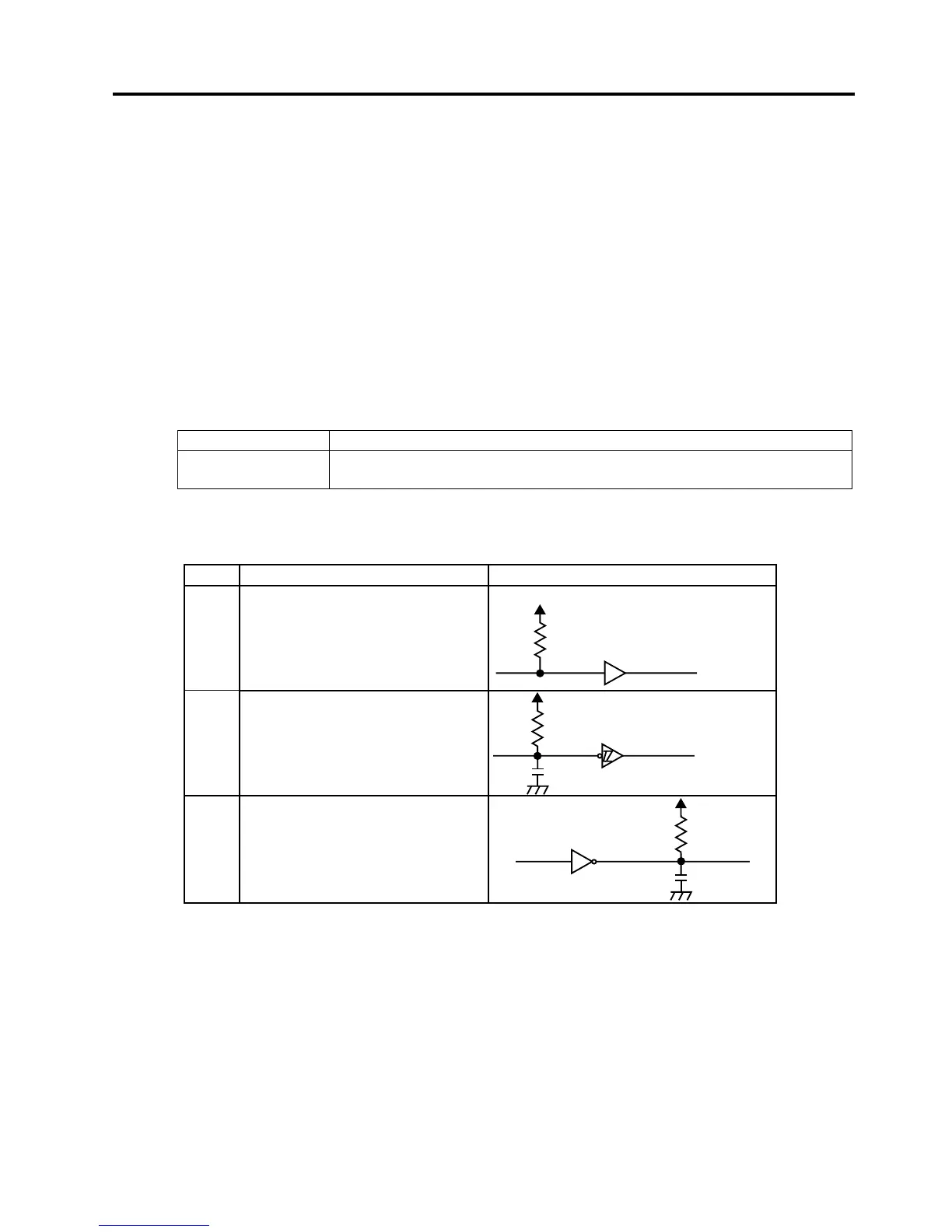

h Input/Output circuit configuration and Input/Output conditions

Type

Loading...

Loading...