Spartan-6 FPGA Power Management www.xilinx.com 23

UG394 (v1.1) September 4, 2012

Post-Configuration CRC Limitations When Using Suspend Mode

Several design options are possible:

1. Do not use the post-configuration CRC feature when the suspend mode feature is

enabled and vice versa.

2. Always reprogram the device when a CRC error occurs.

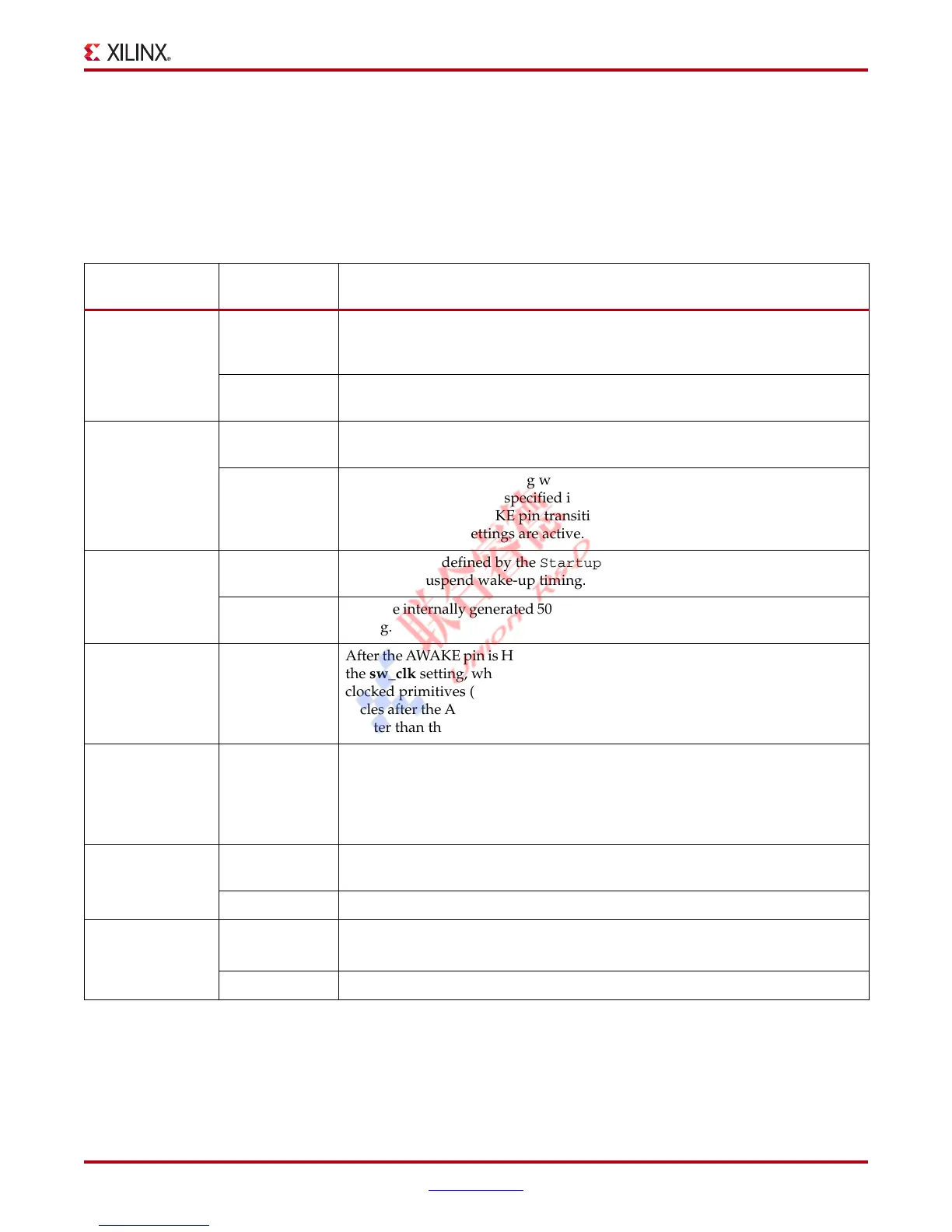

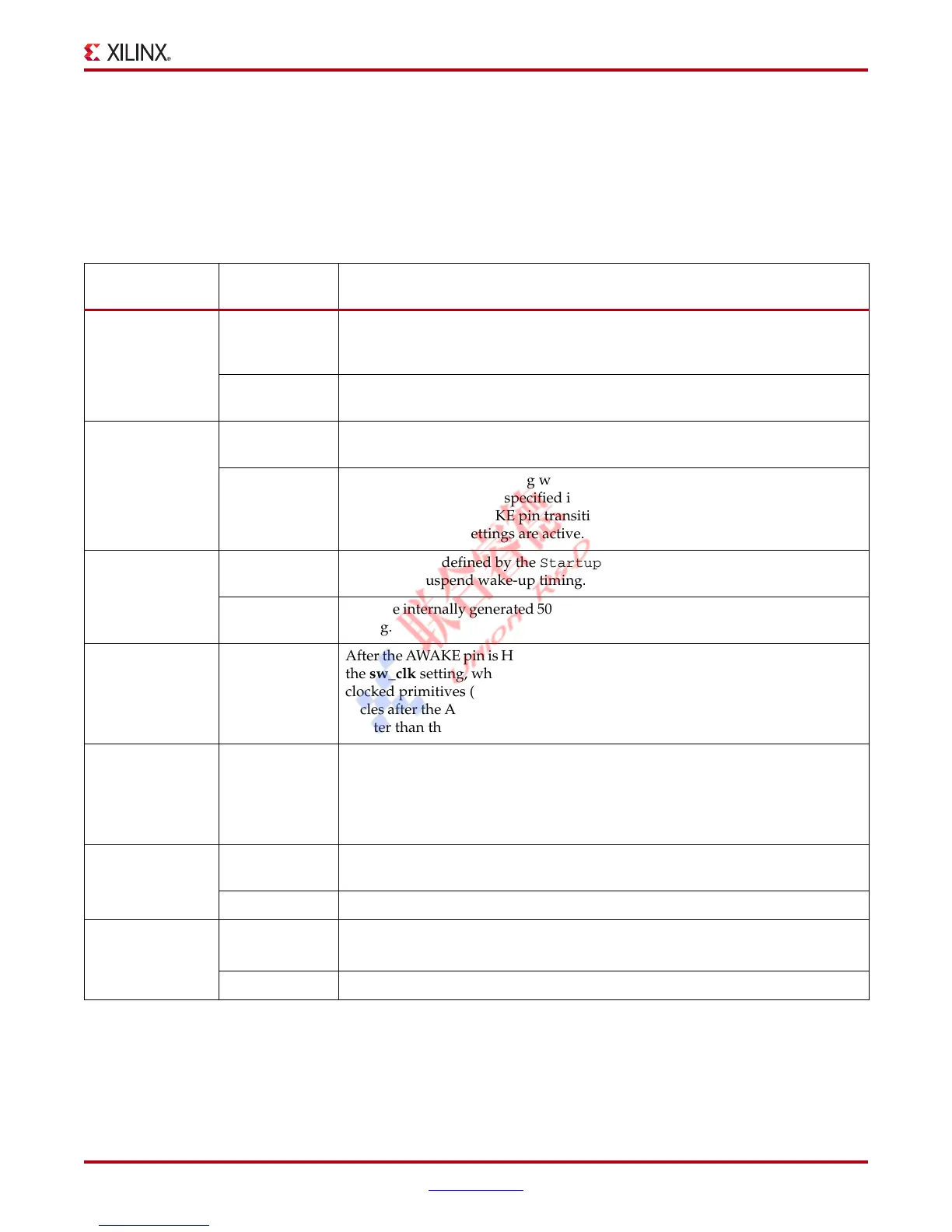

Table 1-7 summarizes the various bitstream options associated with suspend mode.

Table 1-7: Suspend Mode Bitstream Generator Options

Suspend Mode

Bitstream Options

Options

(Default) Description

drive_awake

No

(Default)

If suspend mode is enabled, indicates the present status on AWAKE using an

open-drain output. An external pull-up resistor or High signal is required to exit

SUSPEND mode.

Yes

If suspend mode is enabled, indicates the current status by actively driving the

AWAKE output.

en_sw_gsr No

(Default)

The state of all clocked primitives in the FPGA is preserved.

Yes

Pulses the GSR signal during wake-up, setting or resetting all clocked

primitives, as originally specified in the FPGA application. The GSR pulse

occurs before the AWAKE pin transitions High and before the sw_gwe_cycle

and sw_gts_cycle settings are active.

sw_clk StartupClk

(Default)

Uses the clock defined by the StartupClk bitstream generator setting to

control the suspend wake-up timing.

InternalClk

Uses the internally generated 50 MHz oscillator to control the suspend wake-up

timing.

sw_gwe_cycle

1,..,5,...,1024

Default is 5

After the AWAKE pin is High, indicates the number of clock cycles as defined by

the sw_clk setting, when the global write-protect lock is released for writable

clocked primitives (flip-flops, block RAM, etc.). The default value is five clock

cycles after the AWAKE pin transitions High. Generally, this value is equal to or

greater than the sw_gts_cycle setting.

sw_gts_cycle

1,..,4,...,1024

Default is 4

After the AWAKE pin is High, indicates the number of clock cycles as defined by

the sw_clk setting, when the I/O pins switch from their SUSPEND Attribute,

page 16 settings back to their normal functions. The default value is four clock

cycles after the AWAKE pin goes High. Generally, this value is equal to or less

than the sw_gwe_cycle setting.

multipin_wakeup No

(Default)

Disables multi-pin wake-up.

Yes Enables multi-pin wake-up.

wakeup_mask 0x00

(Default)

Masks out SCP<7:0>

<hex string> FF enables SCP<7:0>, 0F enables SCP<3:0>.

Loading...

Loading...