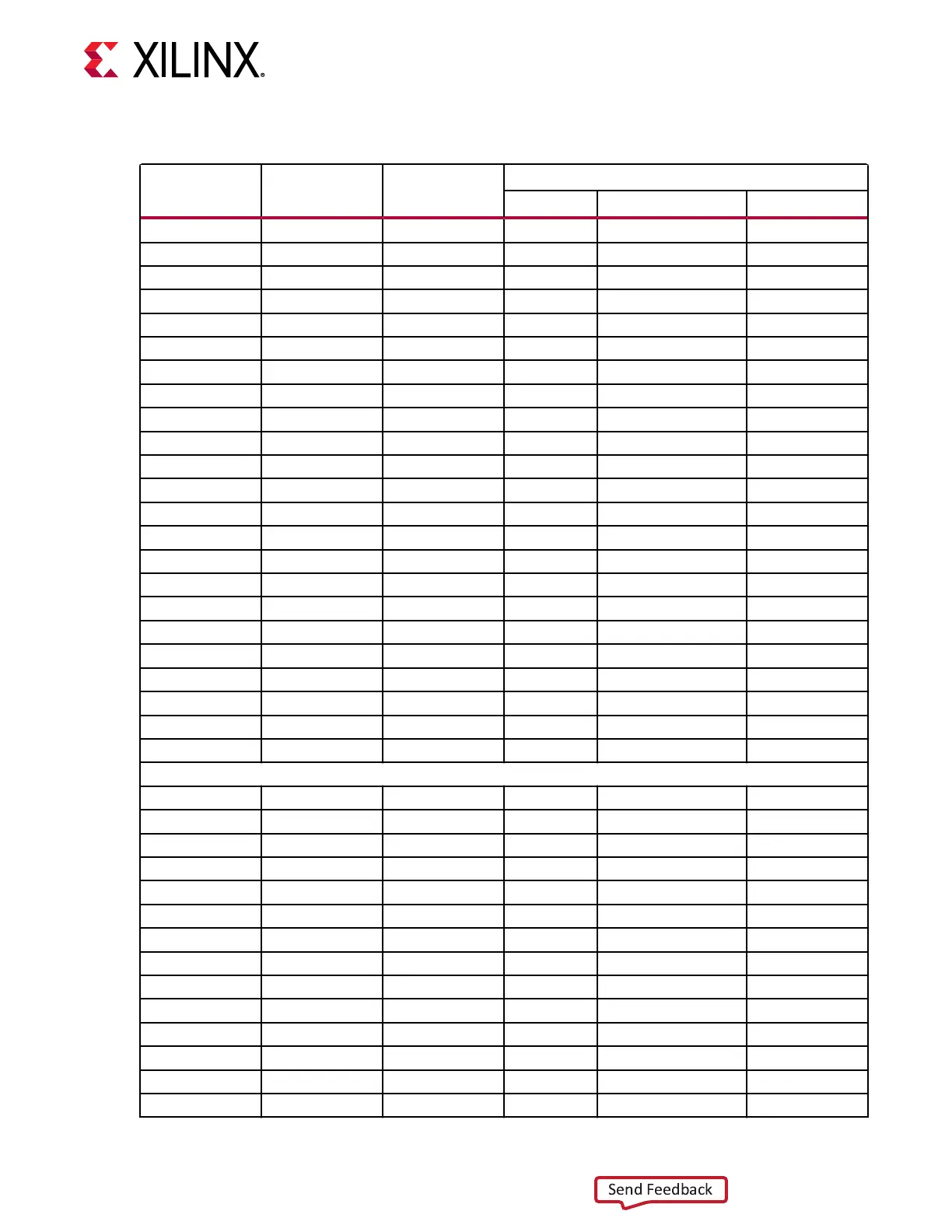

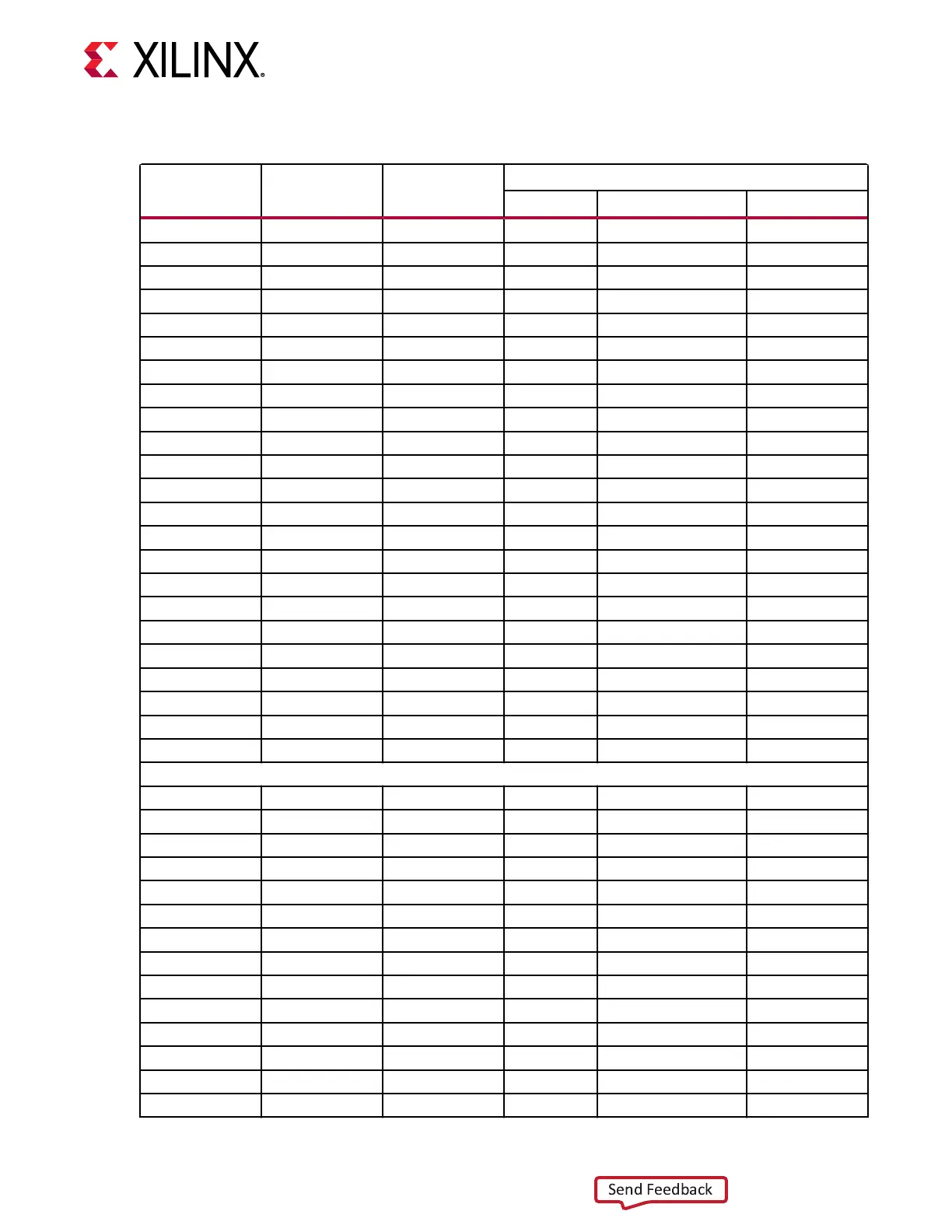

Table 6: DDR4 Memory 72-bit I/F to FPGA U1 Banks 64, 65, and 66 (cont'd)

FPGA (U1) Pin

Schematic Net

Name

I/O Standard

Component Memory

Pin # Pin Name Ref. Des.

BH32 PL_DDR4_DM6_B POD12_DCI E2 NF/UDM_B/UDBI_B U18

BF31 PL_DDR4_DQ56 POD12_DCI A3 DQ8 U73

BH30 PL_DDR4_DQ57 POD12_DCI B8 DQ9 U73

BJ31 PL_DDR4_DQ58 POD12_DCI C3 DQ10 U73

BG32 PL_DDR4_DQ59 POD12_DCI C7 DQ11 U73

BH31 PL_DDR4_DQ60 POD12_DCI C2 DQ12 U73

BF32 PL_DDR4_DQ61 POD12_DCI C8 DQ13 U73

BH29 PL_DDR4_DQ62 POD12_DCI D3 DQ14 U73

BF33 PL_DDR4_DQ63 POD12_DCI D7 DQ15 U73

BJ29 PL_DDR4_DQS7_T DIFF_POD12_DCI B7 UDQS_T U73

BK30 PL_DDR4_DQS7_C DIFF_POD12_DCI A7 UDQS_C U73

BG29 PL_DDR4_DM7_B POD12_DCI E2 NF/UDM_B/UDBI_B U73

BN51 PL_DDR4_DQ64 POD12_DCI A3 DQ8 U17

BM52 PL_DDR4_DQ65 POD12_DCI B8 DQ9 U17

BN50 PL_DDR4_DQ66 POD12_DCI C3 DQ10 U17

BL52 PL_DDR4_DQ67 POD12_DCI C7 DQ11 U17

BM48 PL_DDR4_DQ68 POD12_DCI C2 DQ12 U17

BL53 PL_DDR4_DQ69 POD12_DCI C8 DQ13 U17

BN49 PL_DDR4_DQ70 POD12_DCI D3 DQ14 U17

BL51 PL_DDR4_DQ71 POD12_DCI D7 DQ15 U17

BM49 PL_DDR4_DQS8_T DIFF_POD12_DCI B7 UDQS_T U17

BM50 PL_DDR4_DQS8_C DIFF_POD12_DCI A7 UDQS_C U17

BP48 PL_DDR4_DM8_B POD12_DCI E2 NF/UDM_B/UDBI_B U17

COMMON

BF50 PL_DDR4_A0 SSTL12_DCI P3 A0 U17-U19 U73-U74

BD51 PL_DDR4_A1 SSTL12_DCI P7 A1 U17-U19 U73-U74

BG48 PL_DDR4_A2 SSTL12_DCI R3 A2 U17-U19 U73-U74

BE50 PL_DDR4_A3 SSTL12_DCI N7 A3 U17-U19 U73-U74

BE49 PL_DDR4_A4 SSTL12_DCI N3 A4 U17-U19 U73-U74

BE51 PL_DDR4_A5 SSTL12_DCI P8 A5 U17-U19 U73-U74

BF53 PL_DDR4_A6 SSTL12_DCI P2 A6 U17-U19 U73-U74

BG50 PL_DDR4_A7 SSTL12_DCI R8 A7 U17-U19 U73-U74

BF51 PL_DDR4_A8 SSTL12_DCI R2 A8 U17-U19 U73-U74

BG47 PL_DDR4_A9 SSTL12_DCI R7 A9 U17-U19 U73-U74

BF47 PL_DDR4_A10 SSTL12_DCI M3 A10/AP U17-U19 U73-U74

BG49 PL_DDR4_A11 SSTL12_DCI T2 A11 U17-U19 U73-U74

BF48 PL_DDR4_A12 SSTL12_DCI M7 A12/BC_B U17-U19 U73-U74

BF52 PL_DDR4_A13 SSTL12_DCI T8 A13 U17-U19 U73-U74

Chapter 3: Board Component Descriptions

UG1302 (v1.0) December 21, 2018 www.xilinx.com

VCU128 Board User Guide 23

Loading...

Loading...