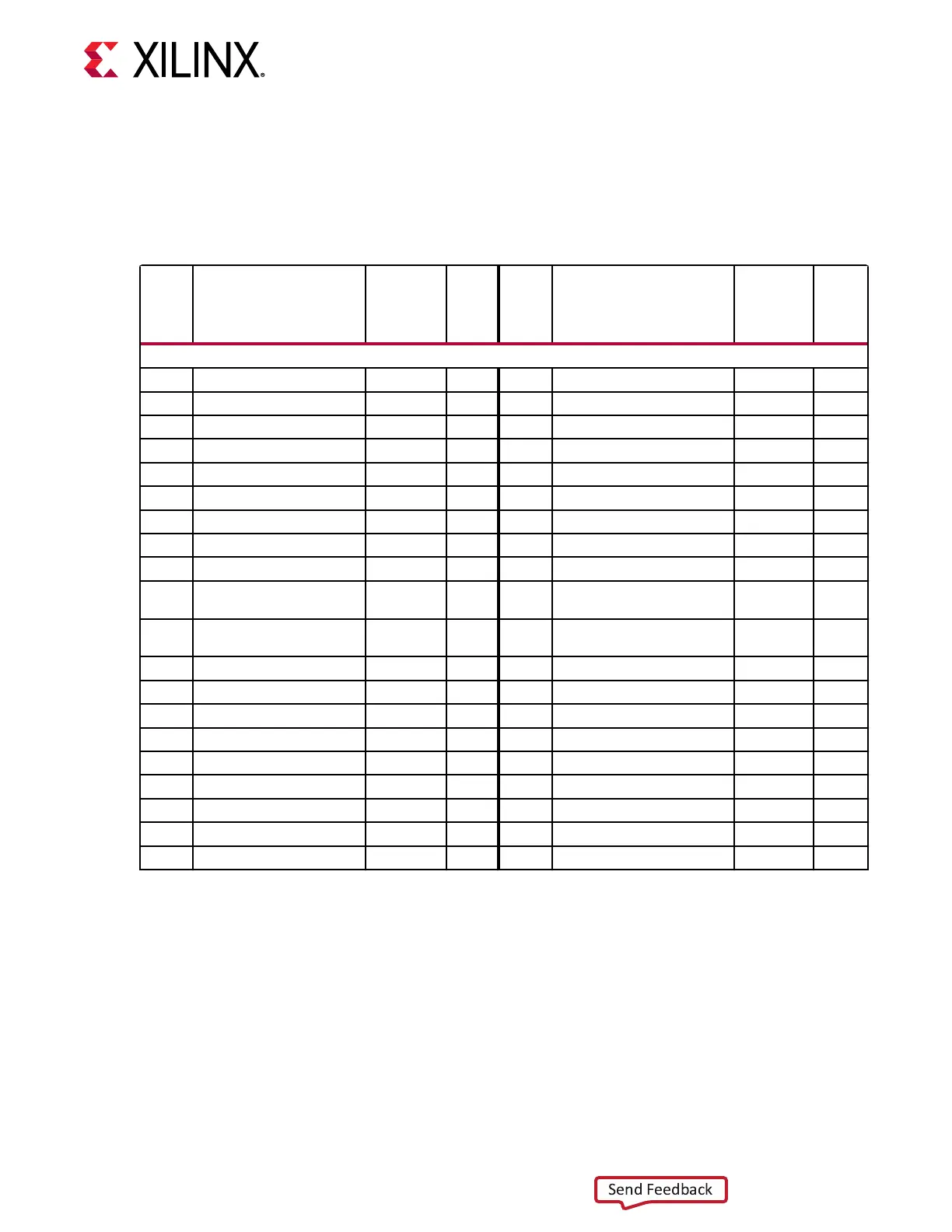

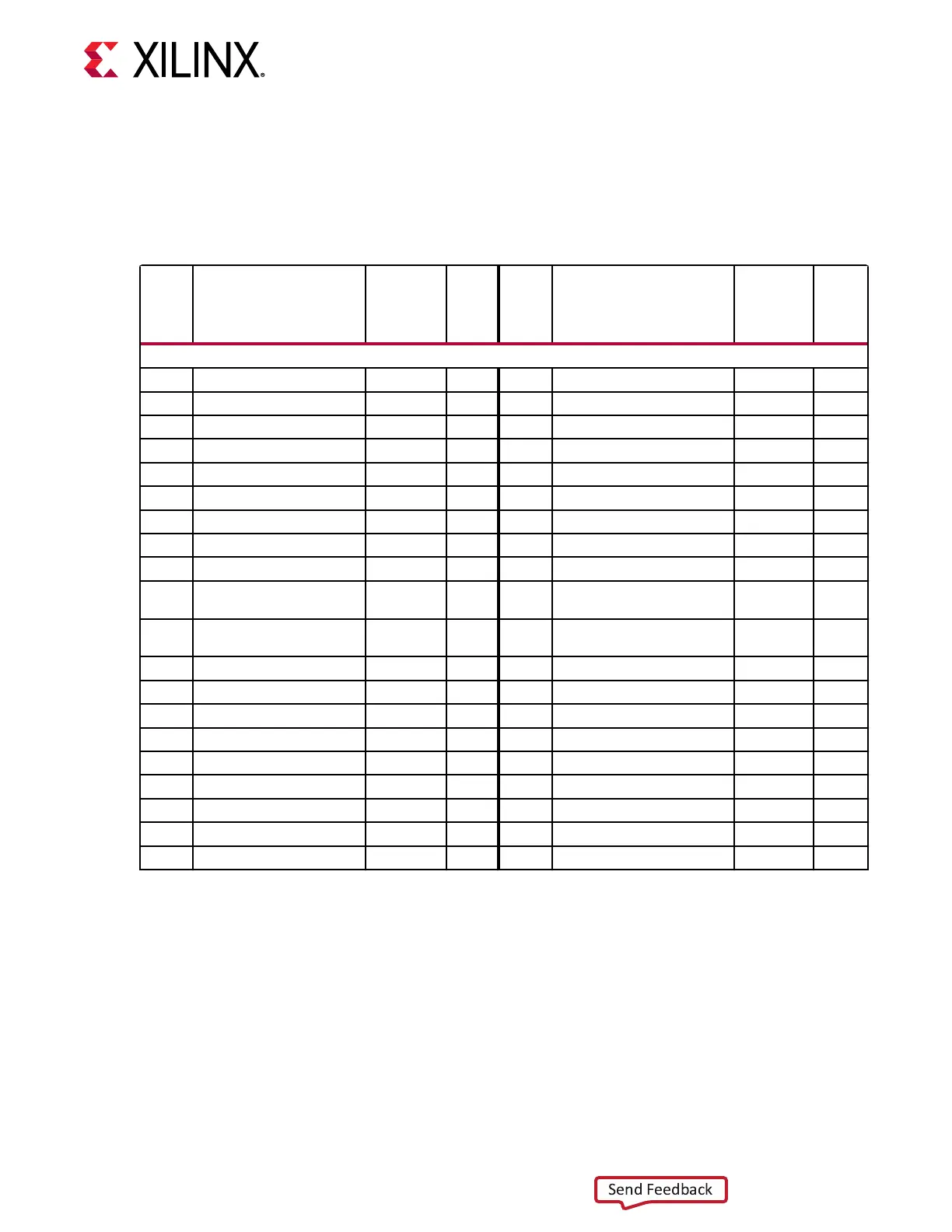

J18 VITA 57.4 FMCP HSCP Connections

The FMCP J18 connecons to FPGA U1 are listed in the following table. The net names shown

in the table are connected to FMCP HSCP J18 pins.

Table 31: J18 VITA 57.4 FMCP HSCP Connections

J18

FMCP

HSCP

Pin

Schematic

Net Name

I/O

Standard

FPGA

(U1)

Pin

J18

FMCP

HSCP

Pin

Schematic Net Name

I/O

Standard

FPGA

(U1)

Pin

J18 Sections A/B Connections to FPGA U1

A2 FMCP_HSPC_DP1_M2C_P LVDS BB51 B1 NC

A3 FMCP_HSPC_DP1_M2C_N LVDS BB52 B4 FMCP_HSPC_DP9_M2C_P LVDS AT51

A6 FMCP_HSPC_DP2_M2C_P LVDS BA53 B5 FMCP_HSPC_DP9_M2C_N LVDS AT52

A7 FMCP_HSPC_DP2_M2C_N LVDS BA54 B8 FMCP_HSPC_DP8_M2C_P LVDS AU53

A10 FMCP_HSPC_DP3_M2C_P LVDS BA49 B9 FMCP_HSPC_DP8_M2C_N LVDS AU54

A11 FMCP_HSPC_DP3_M2C_N LVDS BA50 B12 FMCP_HSPC_DP7_M2C_P LVDS AV51

A14 FMCP_HSPC_DP4_M2C_P LVDS AY51 B13 FMCP_HSPC_DP7_M2C_N LVDS AV52

A15 FMCP_HSPC_DP4_M2C_N LVDS AY52 B16 FMCP_HSPC_DP6_M2C_P LVDS AW49

A18 FMCP_HSPC_DP5_M2C_P LVDS AW53 B17 FMCP_HSPC_DP6_M2C_N LVDS AW50

A19 FMCP_HSPC_DP5_M2C_N LVDS AW54 B20 FMCP_HSPC_GBTCLK1_M2C_

P

LVDS AR40

A22 FMCP_HSPC_DP1_C2M_P LVDS BC44 B21 FMCP_HSPC_GBTCLK1_M2C_

N

LVDS AR41

A23 FMCP_HSPC_DP1_C2M_N LVDS BC45 B24 FMCP_HSPC_DP9_C2M_P LVDS AT46

A26 FMCP_HSPC_DP2_C2M_P LVDS BB46 B25 FMCP_HSPC_DP9_C2M_N LVDS AT47

A27 FMCP_HSPC_DP2_C2M_N LVDS BB47 B28 FMCP_HSPC_DP8_C2M_P LVDS AU48

A30 FMCP_HSPC_DP3_C2M_P LVDS BA44 B29 FMCP_HSPC_DP8_C2M_N LVDS AU49

A31 FMCP_HSPC_DP3_C2M_N LVDS BA45 B32 FMCP_HSPC_DP7_C2M_P LVDS AU44

A34 FMCP_HSPC_DP4_C2M_P LVDS AY46 B33 FMCP_HSPC_DP7_C2M_N LVDS AU45

A35 FMCP_HSPC_DP4_C2M_N LVDS AY47 B36 FMCP_HSPC_DP6_C2M_P LVDS AV46

A38 FMCP_HSPC_DP5_C2M_P LVDS AW44 B37 FMCP_HSPC_DP6_C2M_N LVDS AV47

A39 FMCP_HSPC_DP5_C2M_N LVDS AW45 B40 NC

Chapter 3: Board Component Descriptions

UG1302 (v1.0) December 21, 2018 www.xilinx.com

VCU128 Board User Guide 81

Loading...

Loading...