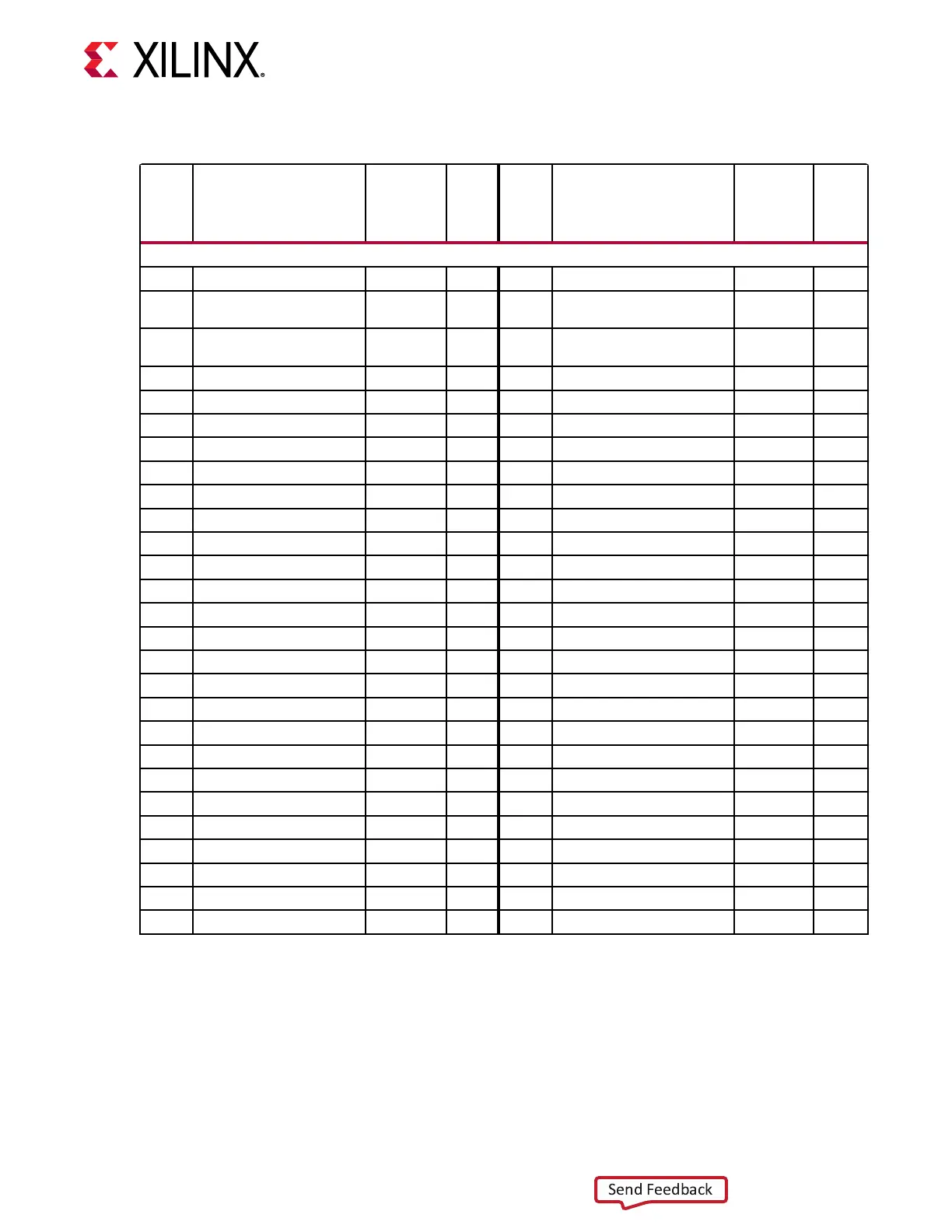

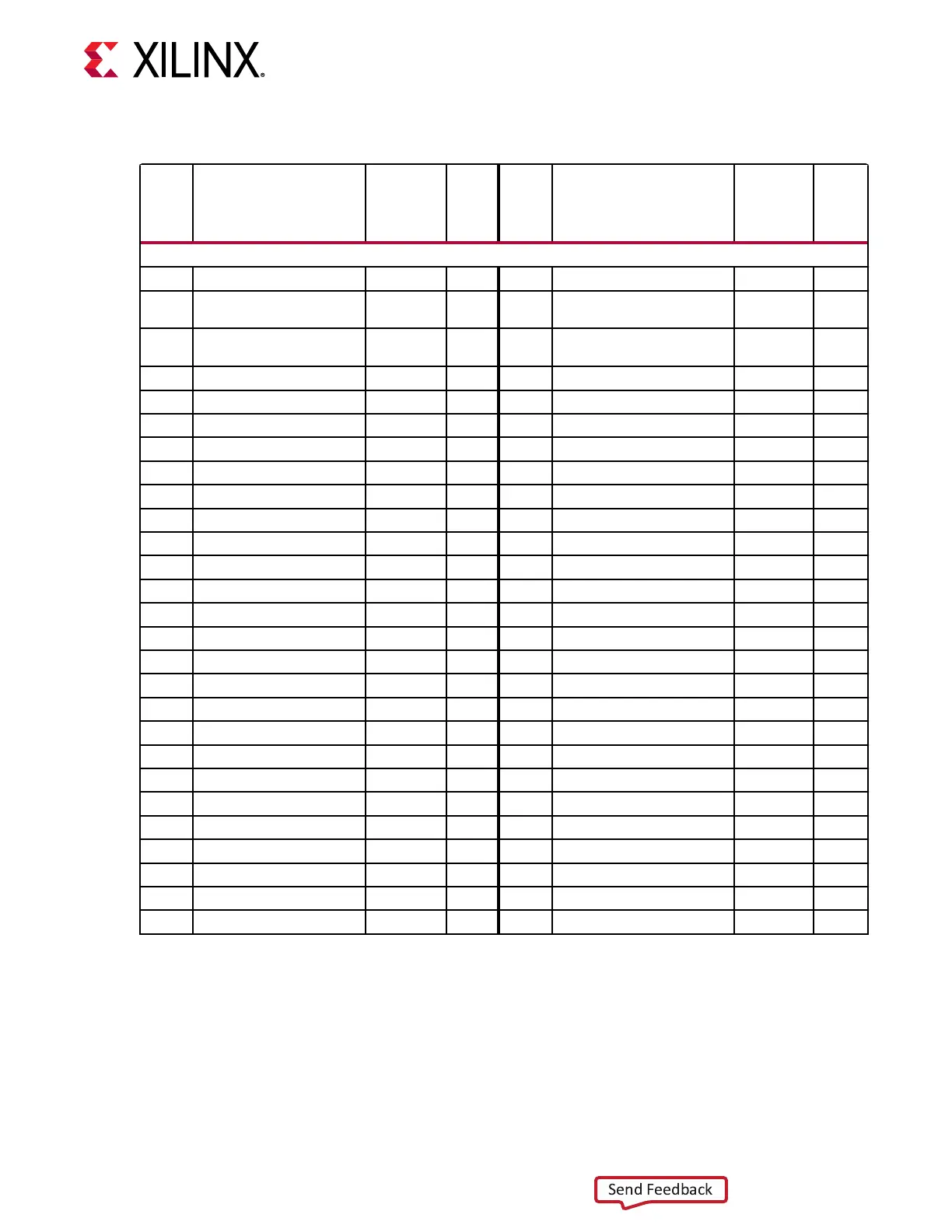

Table 31: J18 VITA 57.4 FMCP HSCP Connections (cont'd)

J18

FMCP

HSCP

Pin

Schematic

Net Name

I/O

Standard

FPGA

(U1)

Pin

J18

FMCP

HSCP

Pin

Schematic Net Name

I/O

Standard

FPGA

(U1)

Pin

J18 Sections C/D Connections to FPGA U1

C2 FMCP_HSPC_DP0_C2M_P LVDS BC53 D1 VADJ_PG

C3 FMCP_HSPC_DP0_C2M_N LVDS BC54 D4 FMCP_HSPC_GBTCLK0_M2C_

P

LVDS AV42

C6 FMCP_HSPC_DP0_M2C_P LVDS BC48 D5 FMCP_HSPC_GBTCLK0_M2C_

N

LVDS AV43

C7 FMCP_HSPC_DP0_M2C_N LVDS BC49 D8 FMCP_HSPC_LA01_CC_P LVDS F26

C10 FMCP_HSPC_LA06_P LVDS E22 D9 FMCP_HSPC_LA01_CC_N LVDS F25

C11 FMCP_HSPC_LA06_N LVDS D22 D11 FMCP_HSPC_LA05_P LVDS H27

C14 FMCP_HSPC_LA10_P LVDS B23 D12 FMCP_HSPC_LA05_N LVDS G27

C15 FMCP_HSPC_LA10_N LVDS A23 D14 FMCP_HSPC_LA09_P LVDS E26

C18 FMCP_HSPC_LA14_P LVDS C23 D15 FMCP_HSPC_LA09_N LVDS D26

C19 FMCP_HSPC_LA14_N LVDS B22 D17 FMCP_HSPC_LA13_P LVDS A25

C22 FMCP_HSPC_LA18_CC_P LVDS E19 D18 FMCP_HSPC_LA13_N LVDS A24

C23 FMCP_HSPC_LA18_CC_N LVDS E18 D20 FMCP_HSPC_LA17_CC_P LVDS F18

C26 FMCP_HSPC_LA27_P LVDS E21 D21 FMCP_HSPC_LA17_CC_N LVDS E17

C27 FMCP_HSPC_LA27_N LVDS D21 D23 FMCP_HSPC_LA23_P LVDS B21

C30 FMCP_HSPC_IIC_SCL D24 FMCP_HSPC_LA23_N LVDS B20

C31 FMCP_HSPC_IIC_SDA D26 FMCP_HSPC_LA26_P LVDS D17

C34 GA0 = 0 = GND D27 FMCP_HSPC_LA26_N LVDS D16

C35 VCC12_SW D29 FMCP_HSPC_TCK_BUF

C37 VCC12_SW D30 FPGA_TDO_FMC_TDI_BUF

C39 UTIL_3V3 D31 FMCP_HSPC_TDO_HPC1_TDI

D32 UTIL_3V3

D33 FMCP_HSPC_TMS_BUF

D34 NC

D35 GA1 = 0 = GND

D36 UTIL_3V3

D38 UTIL_3V3

D40 UTIL_3V3

Chapter 3: Board Component Descriptions

UG1302 (v1.0) December 21, 2018 www.xilinx.com

VCU128 Board User Guide 82

Loading...

Loading...