56 www.xilinx.com VC7222 IBERT Getting Started Guide

UG971 (v5.0) June 12, 2014

Chapter 3: Creating the GTZ IBERT Core

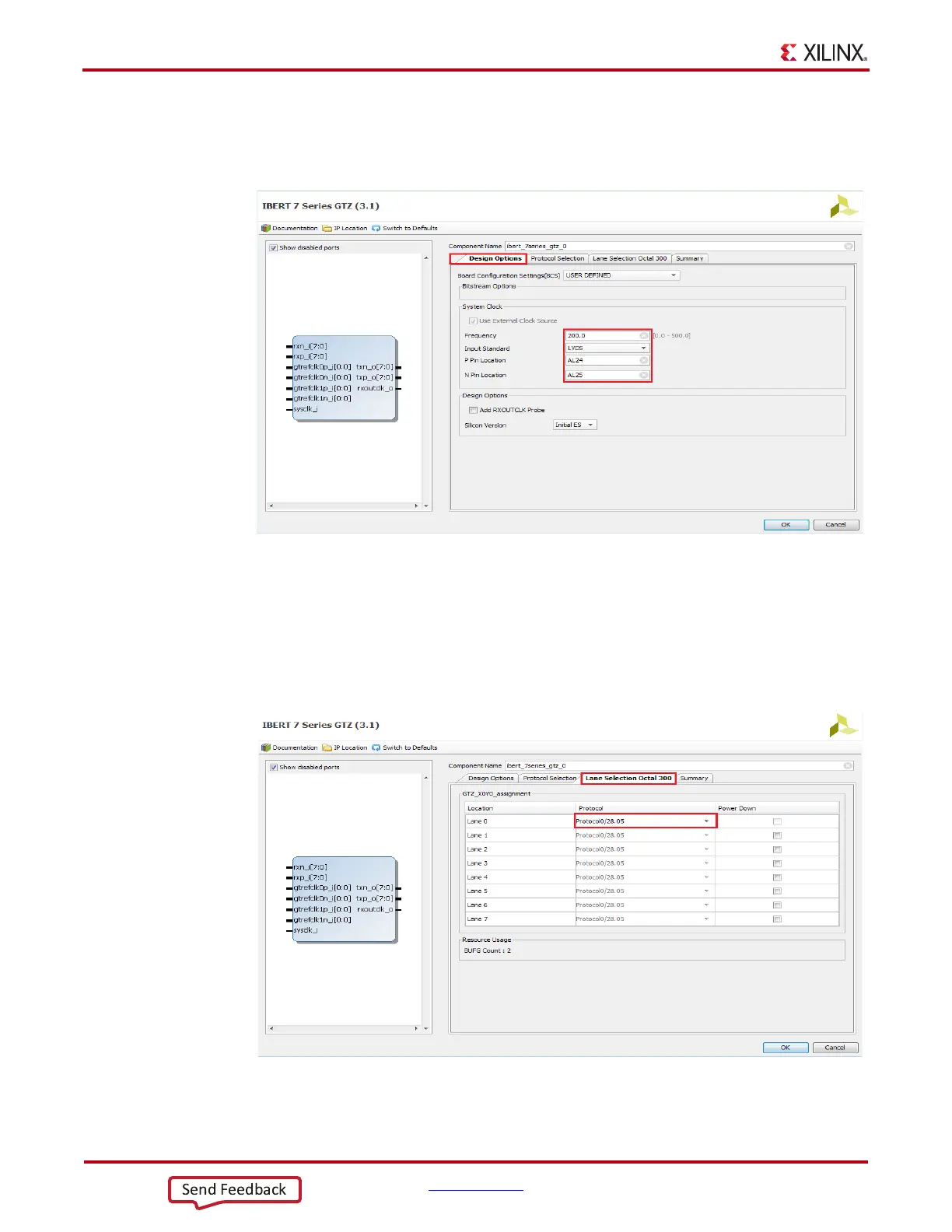

2. A Customize IP window opens. In the Design Options tab, set the system clock

frequency to 200 MHz, the input Standard to LVDS, the P and N Pin location to AL24

and AL25, respectively (Figure 3-2).

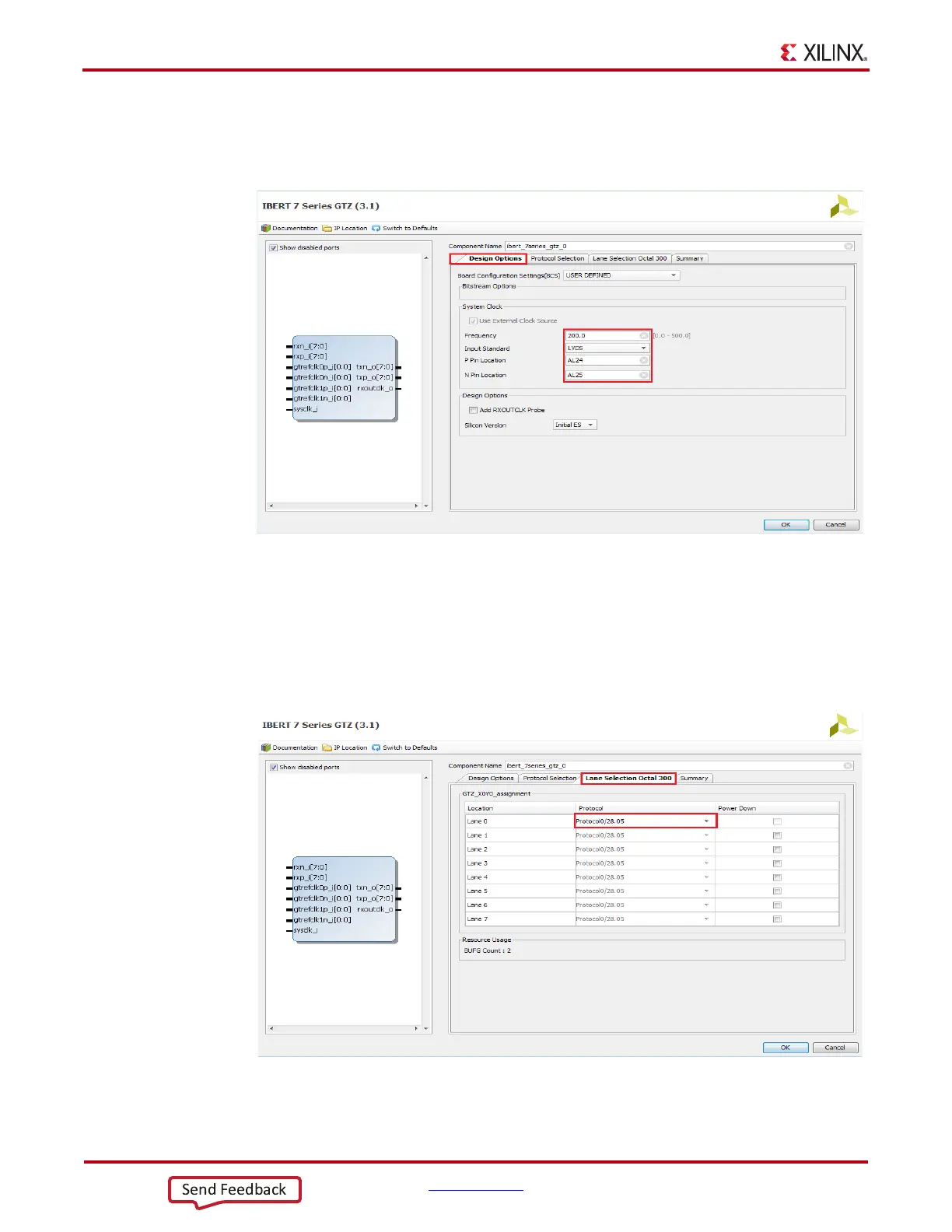

3. In the Protocol Selection tab, set the Line Rate to 28.05 Gbps, and the reference

frequency to 255 MHz (Figure 3-3).

Note:

The reference frequency can be set to any of the available options in the drop-down

menu. The same frequency should be set in the setup_scm2_freq_00_xx.tcl script by

modifying the set frequency statement.

X-Ref Target - Figure 3-2

Figure 3-2: Customize IP - Design Options

X-Ref Target - Figure 3-3

Figure 3-3: Customize IP - Protocol Selection

Loading...

Loading...