ZCU111 Board User Guide 72

UG1271 (v1.1) August 6, 2018 www.xilinx.com

Chapter 3: Board Component Descriptions

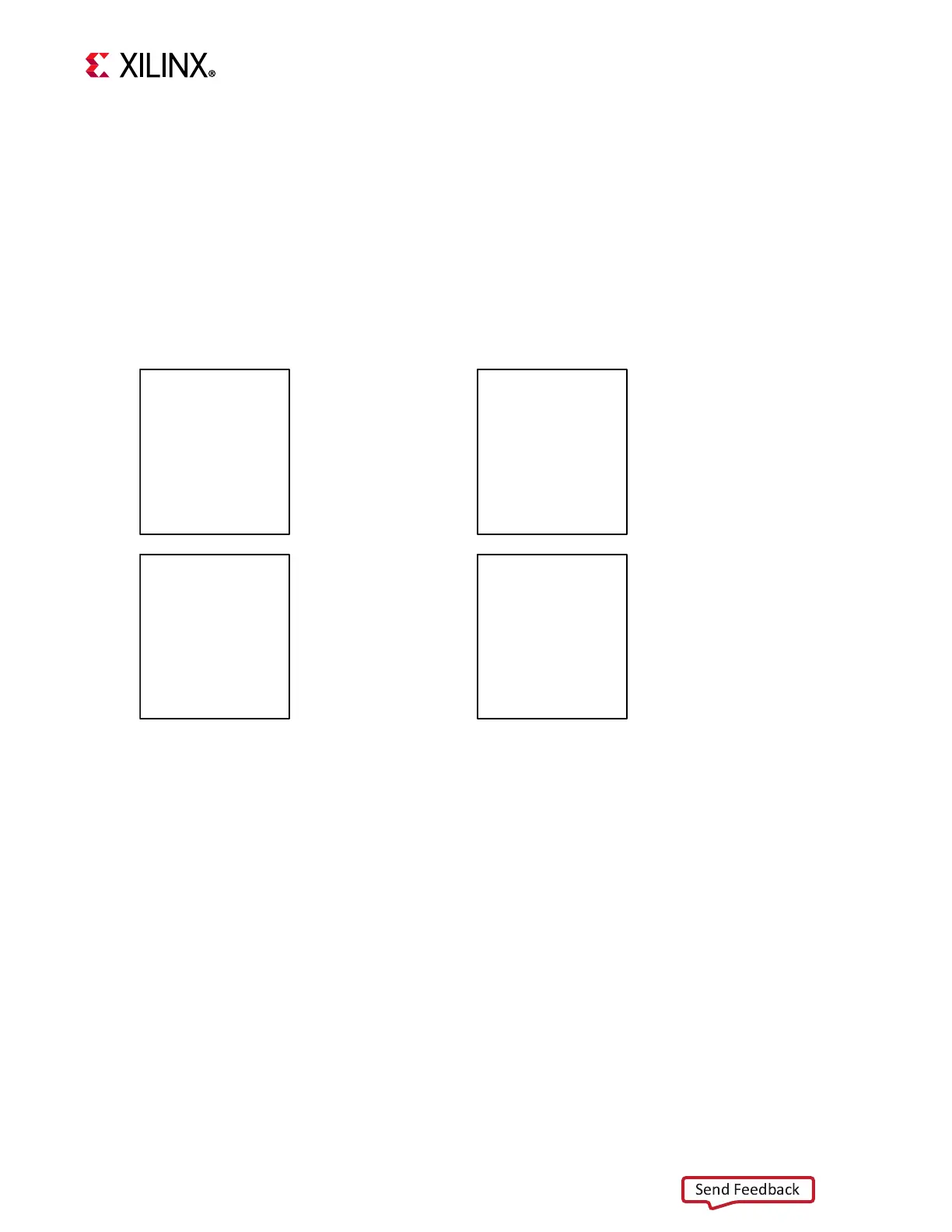

• MGTREFCLK1 - USER_SMA_MGT_CLOCK_C_P/N

• Contains four GTY transceivers allocated to FMCP_HSPC_DP[4:7] TX/RX

• Quad 131:

• MGTREFCLK0 - FMCP_HSPC_GBTCLK2_M2C_C_P/N

• MGTREFCLK1 - not connected

• Contains four GTY transceivers allocated to FMCP_HSPC_DP[8:11] TX/RX

Figure 3-29 shows the MGTY assignments.

FMCP HSPC

Twelve MGTs are provided by PL-side MGT banks 129, 130, and 131. Available MGT

reference clocks include the FMC defined GBT clocks 0, 1 and 2, a programmable SI570

clock and an SMA clock.

X-Ref Target - Figure 3-29

Figure 3-29: GTY Bank Assignments

BANK 129

FMCP_HSPC_DP0

FMCP_HSPC_DP1

FMCP_HSPC_DP2

FMCP_HSPC_DP3

MGTY_129_0

MGTY_129_1

MGTY_129_2

MGTY_129_3

FMCP_HSPC_GBTCLK0_M2C

USER_MGT_S1570_CLOCK

MGT_129_REFCLK0

MGT_129_REFCLK1

BANK 131

FMCP_HSPC_DP8

FMCP_HSPC_DP9

FMCP_HSPC_DP10

FMCP_HSPC_DP11

MGTY_131_0

MGTY_131_1

MGTY_131_2

MGTY_131_3

FMCP_HSPC_GBTCLK2_M2C

NC

MGT_131_REFCLK0

MGT_131_REFCLK1

BANK 128

SFP0_TX/RX

SFP1_TX/RX

SFP2_TX/RX

SFP3_TX/RX

MGTY_128_0

MGTY_128_1

MGTY_128_2

MGTY_128_3

SFP_S15382_IN1

SFP_S15382_OUT

MGT_128_REFCLK0

MGT_128_REFCLK1

BANK 130

FMCP_HSPC_DP4

FMCP_HSPC_DP5

FMCP_HSPC_DP6

FMCP_HSPC_DP7

MGTY_130_0

MGTY_130_1

MGTY_130_2

MGTY_130_3

FMCP_HSPC_GBTCLK1_M2C

USER_SMA_MGT_CLOCK

MGT_130_REFCLK0

MGT_130_REFCLK1

X20536-071318

Loading...

Loading...