RX-V2500/DSP-AX2500

45

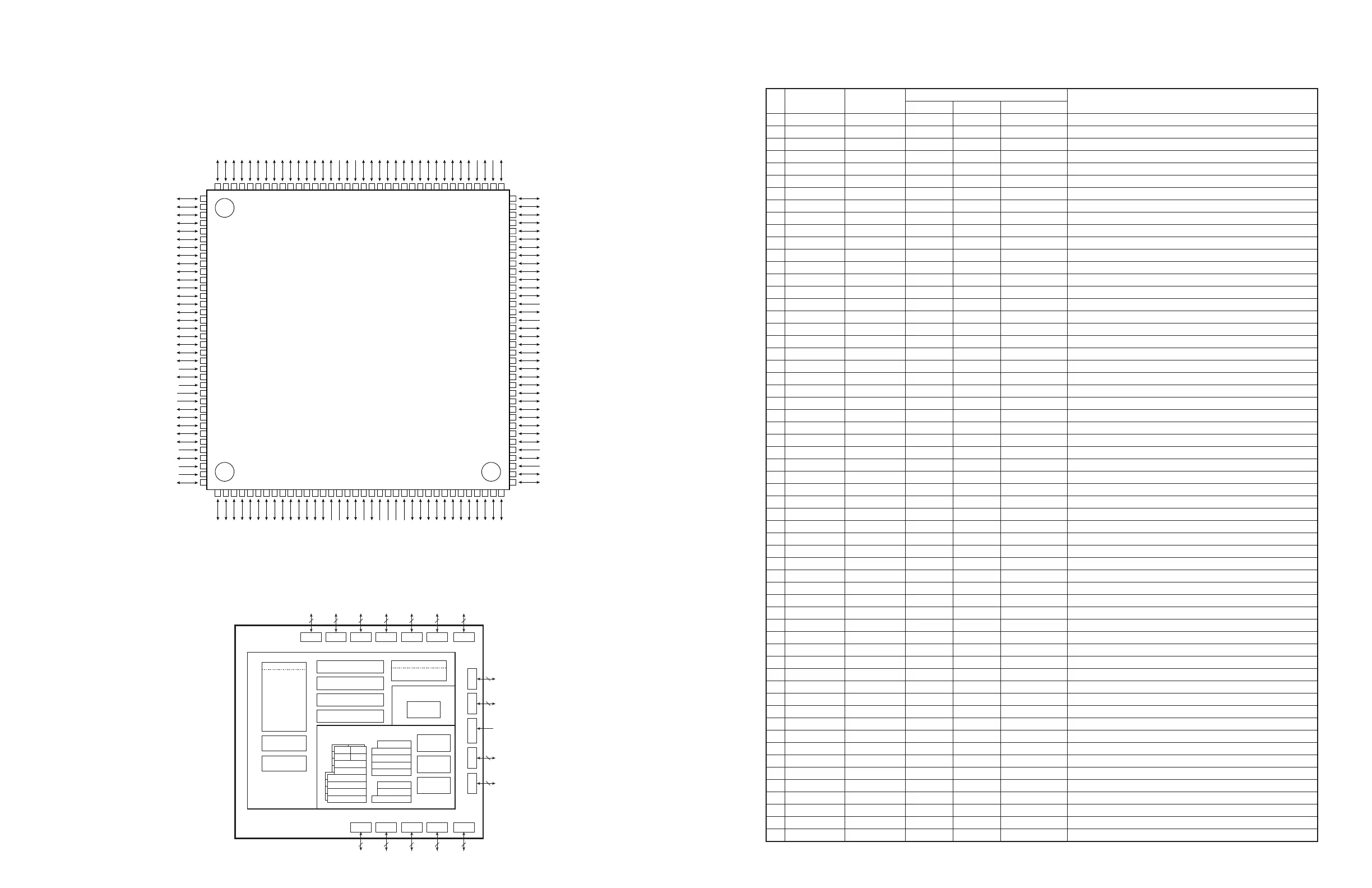

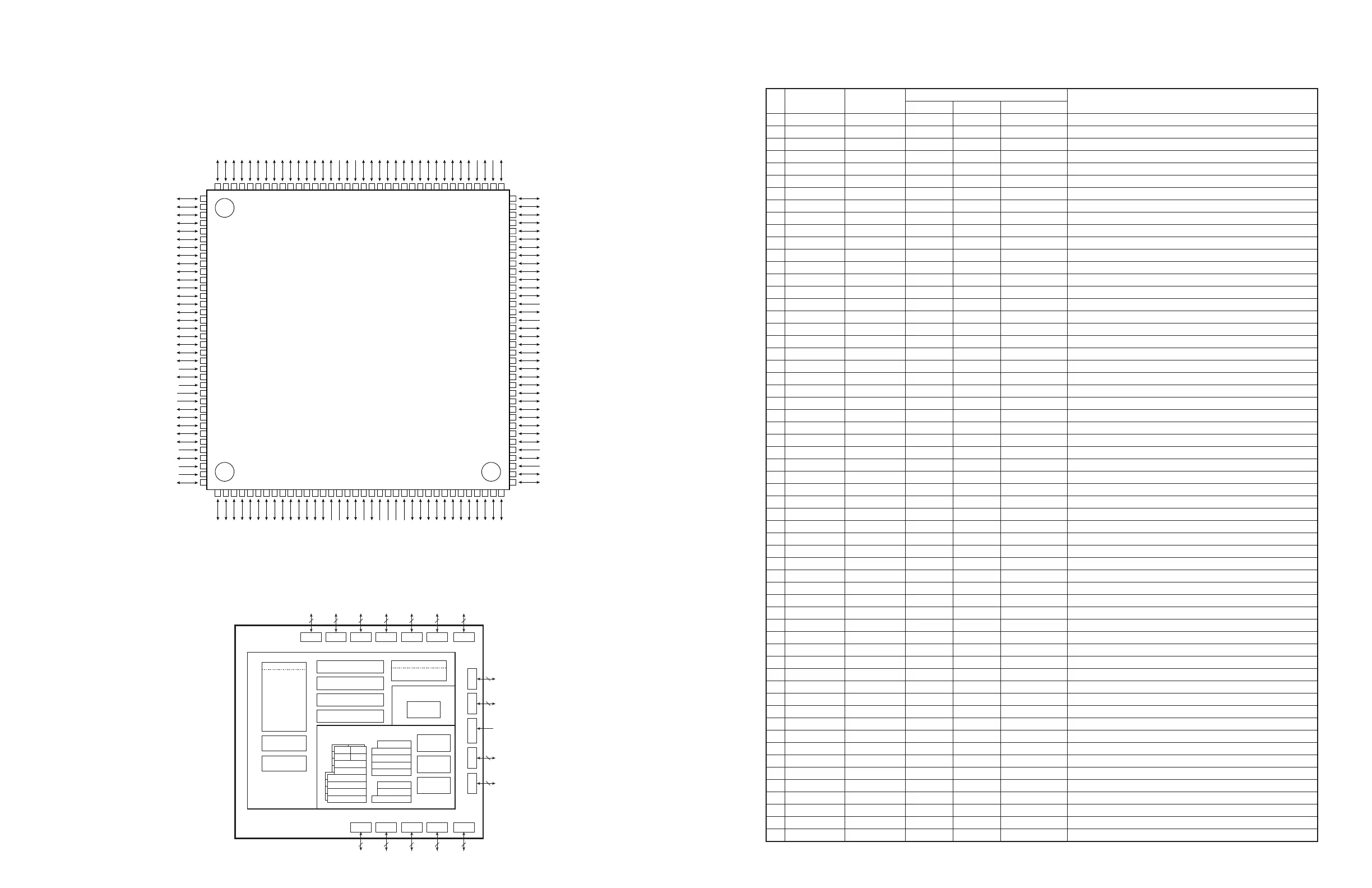

■ IC DATA

108

P11/D9

107

P12/D10

106

P13/D11

105

P14/D12

104

P15/D13/INT3

103

P16/D14/INT4

102

P17/D15/INT5

101

P20/A0

100

P21/A1

99 P22/A2

98 P23/A3

97 P24/A4

96 P25/A5

95 P26/A6

94 P27/A7

93 Vss

92 P30/A8

91 Vcc

90 P120

89 P121

88 P122

87 P123

86 P124

85 P31/A9

84 P32/A10

83 P33/A11

82 P34/A12

81 P35/A13

80 P36/A14

79 P37/A15

78 P40/A16

77 P41/A17

76 Vss

75 P42/A18

74 Vcc

73 P43/A19

72 P44/CS3/A20

71 P45/CS2/A21

70 P46/CS1/A22

69 P47/CS0/A23

68 P125

67 P126

66 P127

65 P50/WRL/WR/CASL

64 P51/WRH/BHE/CASH

63 P52/RD/DW

62 P53/BCLK/ALE/CLKout

61 P130

60 P131

59 Vcc

58 P132

57 Vss

56 P133

55 P54/HLDA/ALE

54 P55/HOLD

53 P56/ALE/RAS

52 P57/RDY

51 P134

50 P135

49 P136

48 P137

47 P60/CTS0/RTS0

46 P61/CLK0

45 P62/RXD0

44 P63/TXD0

43 P64/CTS1/RTS1/CTS0/CLKS1

42 P65/CLK1

41 Vss

40 P66/RXD1

39 Vcc

38 P67/TXD1

37 P70/TXD2/SDA/TA0out

P10/D8

P07/D7

P06/D6

P05/D5

P04/D4

P114

P113

P112

P111

P110

P03/D3

P02/D2

P01/D1

P00/D0

P157

P156

P155

P154

P153

P152

P151

Vss

P150

Vcc

P107/AN7/KI3

P106/AN6/KI2

P105/AN5/KI1

P104/AN4/KI0

P103/AN3

P102/AN2

P101/AN1

Avss

P100/AN0

Vref

Avcc

P97/Adtrg/RxD4/SCL4/STxD4

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

P96/ANEX1/TxD4/SDA4

P95/ANEX0/CLK4

P94/DA1/TB4in/CTS4/RTS4/SS4

P93/DA0/TB3in/CTS3/RTS3/SS3

P92/TB2in/TxD3/SDA3/STxD3

P91/TB1in/RxD3/SCL3

P90/TB0in/CLK3

P146

P145

P144

P143

P142

P141

P140

BYTE

CNVss

P87/Xcin

P86/Xcout

RESET

Xout

Vss

Xin

Vcc

P85/NMI

P84/INT2

P83/INT1

P82/INT0

P81/TA4in/U

P80/TA4out/U

P77/TA3in

P76/TA3out

P75/TA2in/W

P74/TA2out/W

P73/CTS2/RTS2/TA1in/V

P72/CLK2/TA1out/V

P71/RXD2/SCL/TA0in/TB5in

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

M30805SGP

SVP

VCT

SVP

VCT

R2

R3

R0L

R1L

R0H

R1H

A-D Converter (10 bits x 8 channels,

Expendable up to 10 channels)

UART/ Clock Synchronous

SI/O (8 bits x 5 channels)

X-Y Converter

(16 bits x 16 bits)

CRC arithmetic Circuit (CCITT)

(Polynomial: X16+X12+X5+1)

Por t P0

8

RAM

24K

DRAM

Controller

FLG

INTB

ISP

SVF

SVP

VCT

FB

SB

A0

A1

R2

R3

R0L

R1L

R0H

R1H

USP

PC

DRAM

Controller

Multiplier

Registers

Timer

System Clock Generator

Timer TA0 (16 bits)

Timer TA1 (16 bits)

Timer TA2 (16 bits)

Timer TA3 (16 bits)

Timer TA4 (16 bits)

Timer TB0 (16 bits)

Timer TB1 (16 bits)

Timer TB2 (16 bits)

Timer TB3 (16 bits)

Timer TB4 (16 bits)

Timer TB5 (16 bits)

Watchdog Timer

(15 bits)

D-A Converter

(8 bits x 2 channels)

XIN - XOUT

XCIN - XCOUT

Internal Peripheral Functions

I/O Port

Memory

Por t P1

8

Por t P2

8

Por t P3

8

8

Por t P4

Por t P7

8

Por t P8

7

Port P85 Port P9

8

8

Port P10

Por t P5

8

8

Por t P6

Port P15

8

Port P14

7

8

Port P13 Port P12

8

5

Port P11

M16C/80 Series 16-bit CPU core

IC501 : M30805SGP (CONTROL P.C.B)

16bit µ-COM (Main CPU)

IC501 : M30805SGP (CONTROL P.C.B)

16bit µ-COM (Main CPU)

PowerOn Standby

MCUSleep

[

AC OFF

]

RESERVE (Unconnected)

RESERVE (Unconnected)

Limiter control output

Temperature control FAN control ourput

PLL data output for tuner / Transmission clock 4us / LSB first

PLL clock output for tuner

RESERVE (Unconnected)

PLL reception for tuner / Reception clock 20us / LSB first

PLL chip select for tuner

Zone3 MUTE control

Zone2 MUTE control

Headphone MUTE control

Recout SW control (ROHM) clock

Recout SW control (ROHM) data / Clock speed : 20us, MSBF

RS232C FLASH write mode detection / MULTI CH INPUT key detection

BOOT mode detection terminal for YDC

Remote control pulse input 1

Zone2, 3 power key interrupt

POWER DETECT detection

Vertical sync pulse INT

FL enable

RS232C, YDC reception detection

Power relay control

DIR or TI (DA601) interrupt

RESERVE (Unconnected)

Power SW

RESERVE (Unconnected)

RESERVE (Unconnected)

RESERVE

Normal RS-232C asynchronous communication data output / Data transmission terminal for AF220

Normal RS-232C asynchronous communication data input / Data reception terminal for AF220

Normal RS-232C asynchronous communication RTS output / Clock input for AF220

Normal RS-232C asynchronous communication CTS input

Serial data output to DIR, TI (DA601), YSS930, DAC DIR/YSS : 4M, LSBF TI : 1M, MSBF

Serial data input from DIR, TI (DA601), YSS930

Serial data clock output to DIR, TI (DA601), YSS930, DAC

RESERVE (Unconnected)

DIR chip enable

DAC (common to 2ch/8ch) chip enable

YSS930 (common to #0/#1) chip enable

TI decoder DSPDA601 chip enable

YGV/WAIT input

(Unconnected)

(Unconnected)

DIR WCK input (WCK input for Suyama mode write)

RDS CE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

TXDH

CLKH

LIMIT

FAN

TUDA

TUCK

1394INT

PLLR

TUE

Z3MT

Z2MT

HPMT

RCLK

RDATA

BYTE

CNVss

BT232C

BTYDC

/RES

Xout

Vss

Xin

Vcc

NMI

REM

MZ2INT

PDET

VSY

CEF

RXDR

PRY

/INTDSP

/1394CTS

PSW

/1394RTS

RxD1394

TXD1394

TXDR

Vcc

RXDR

Vss

RTS

CTS

TXDD

RXDD

CLKD

IMUTE

/CSDIR

/CSDAC

/CSY

/CSTI

/WAIT

/RAS

/HOLD

/HLDA

SPIRDY

Vss

RDSCE

Vcc

TXD4

CLK4

LIMIT

FAN

TUDA

TUCK

TB0in

PLLR

TUCE

Z3MT

Z2MT

HPMT

RCLK

RDATA

BYTE

CNVss

BT232C

BTYDC

RESET

Xout

Vss

Xin

Vcc

NMI

REM

Z2INT

PDET

VSY

CEF

RXDR

PRY

/INTDSP

P74

PSW

P72/CLK2

RxD2

TXD2

TXDR

Vcc

RXDR

Vss

RTS

CTS

TXDD

RXDD

CLKD

P60

/CSDIR

/CSDAC

/CSY

/CSTI

/WAIT

SPIDRY

Vss

RDSCE

Vcc

SO

SO

DA

DA

O

O

TMR

I

O

O

O

O

O

O

MCU

MCU

I

I

MCU

MCU

MCU

MCU

MCU

IRQ

IRQ

IRQ

IRQ

TMR

O

TMR

O

TMR

I

TMR

O

SI

SO

SO

MCU

SI

MCU

SO

SI

SO

SI

SO

I

O

O

O

O

BUS

BUS

BUS

BUS

I

MCU

O

MCU

O

O

O

O

O

O

I

I

O

O

O

O

O

O

MCU

MCU

I

I

MCU

MCU

MCU

MCU

MCU

I

O

O

I

O

O

O

O

O

I

O

O

I

O

SO

MCU

SI

MCU

SO

SI

O

O

O

I

O

O

O

O

BUS

BUS

BUS

BUS

O

MCU

O

MCU

O

O

O

O

O

O

O

O

O

O [ I ]

O [ I ]

O [ I ]

O

O

MCU

MCU

O

O

MCU

MCU

MCU

MCU

MCU

I

O

O

I

O

O

O

O

O

O

O

O

O

O

O

MCU

O

MCU

O

O

O

O

O

O

O

O

O

O

BUS

BUS

BUS

BUS

O

MCU

O

MCU

No. Port Name

Terminal Name

I/O

Function

Loading...

Loading...