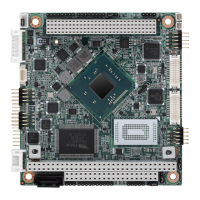

AIMB-240 Series

20 AIMB-240 Series User’s Manual

Multi-monitor support

• Multiple programmable configurations

• Dual independent display

• DVO device support/TV-Out

Dynamic display-mode support

• User definable and extensible

• Embedded video BIOS

• Common port interface support

• Full VGA compatibility

•

1.6.4 DRAM Interface (Intel 852GME)

The 852GME GMCH system memory controller directly supports the following:

• System SDRAM supports 266/333MHz (SSTL_2) DDR SDRAM

• Up to 2 GB (with 256-Mbit technology and two SO-DIMMs) of PC2100/2700 DDR

SDRAM with ECC

1.6.5 PCI Interface

The ICH4 PCI interface provides a 33 MHz, Rev. 2.2 compliant implementation. All PCI

signals are 5V tolerant, except PME#. The ICH2 integrates a PCI arbiter that supports up to

six external PCI bus masters in addition to the internal ICH4 requests.

1.6.6 IDE Interface (Bus Master Capability and Synchronous DMA Mode )

The fast IDE interface supports up to four IDE devices providing an interface for IDE hard

disks and ATAPI devices. Each IDE device can have independent timings. The IDE

interface supports PIO IDE transfers up to 16 Mbytes/sec and Ultra ATA transfers up 100

Mbytes/sec. It does not consume any ISA DMA resources. The IDE interface integrates

16x32-bit buffers for optimal transfers.

The ICH4’s IDE system contains two independent IDE signal channels. They can be

electrically isolated independently. They can be configured to the standard primary and

secondary channels (four devices). There are integrated series resistors on the data and

control lines.

Access to these controllers is provided by two standard IDC 40-pin connectors.