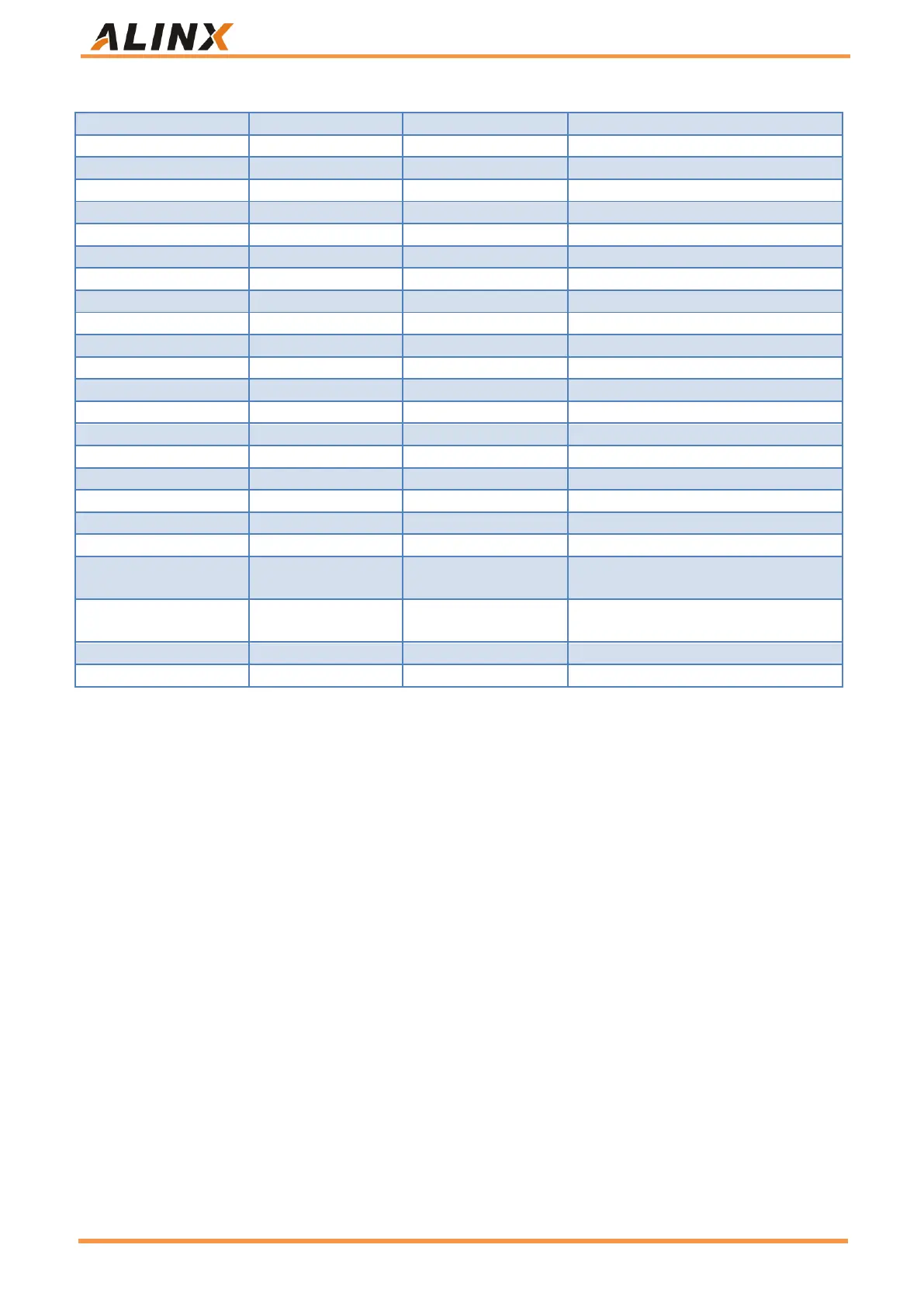

Transceiver Data 6 Input P

Transceiver Data 6 Input N

Transceiver Data 7 Input P

Transceiver Data 7 Input N

Transceiver Data 0 Output P

Transceiver Data 0 Output N

Transceiver Data 1 Output P

Transceiver Data 1 Output N

Transceiver Data 2 Output P

Transceiver Data 2 Output N

Transceiver Data 3 Output P

Transceiver Data 3 Output N

Transceiver Data 4 Output P

Transceiver Data 4 Output N

Transceiver data 5 output P

Transceiver Data 5 Output N

Transceiver Data 6 Output P

Transceiver Data 6 Output N

Transceiver Data 7 Output P

Transceiver Data 7 Output N

Transceiver Reference Clock 0 Input P

Transceiver Reference Clock 0 Input N

Transceiver Reference Clock 1 Input P

Transceiver Reference Clock 1 Input N

Table 18: FMC HPC J12 connector pin assignment

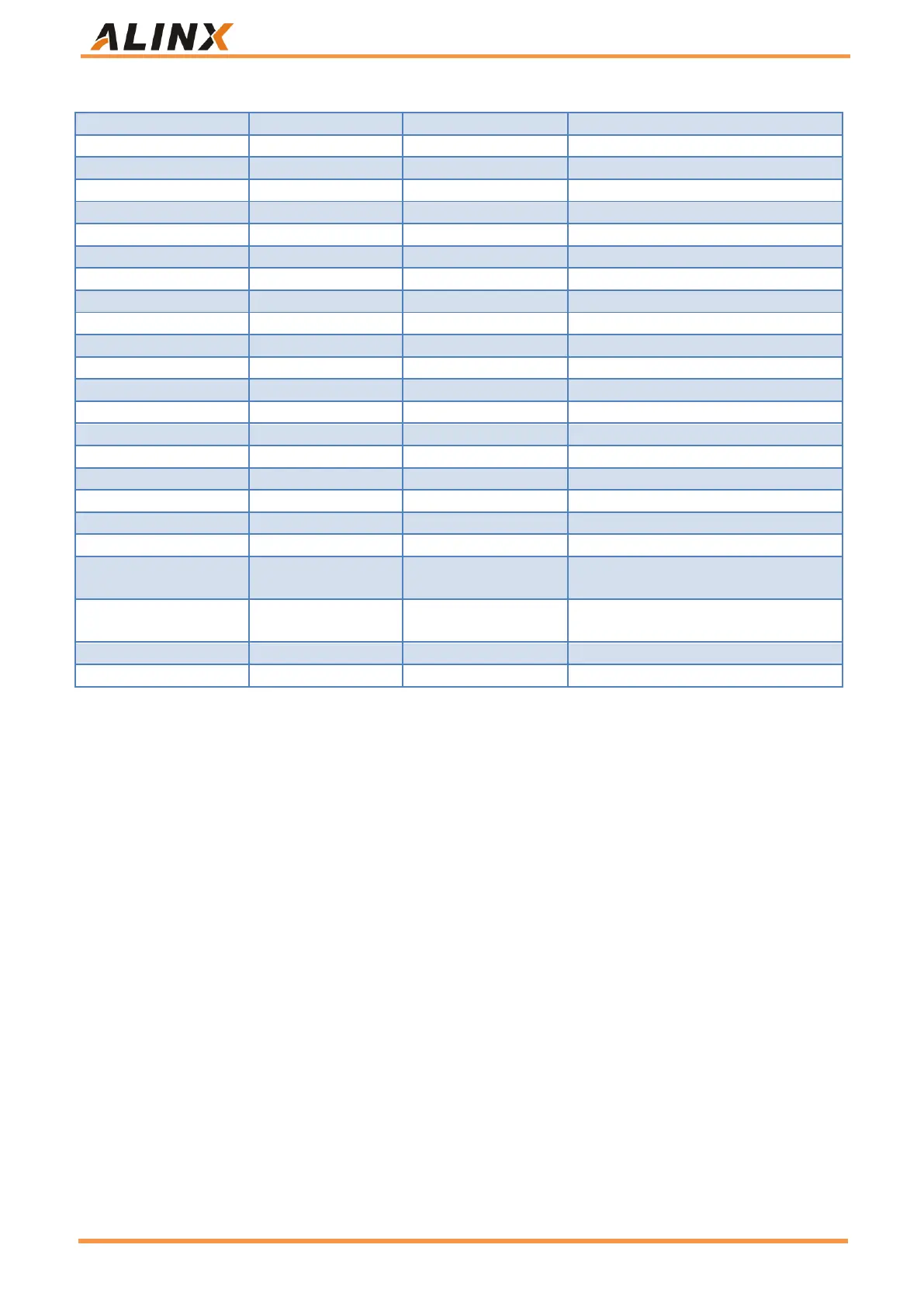

The FMC2 expansion port contains 34 pairs of LA signal differential pairs and 2 pairs of clock signals, which are

connected to the FPGA chips BANK64 and BANK65 respectively. The standard level is 1.8V by default. 8 channels

of high-speed GTY transceiving signals are connected to the IO of FPGA chips BANK224 and BANK225.

The schematic diagram of the FPGA and FMC HPC connector is shown in Figure 20:

Loading...

Loading...