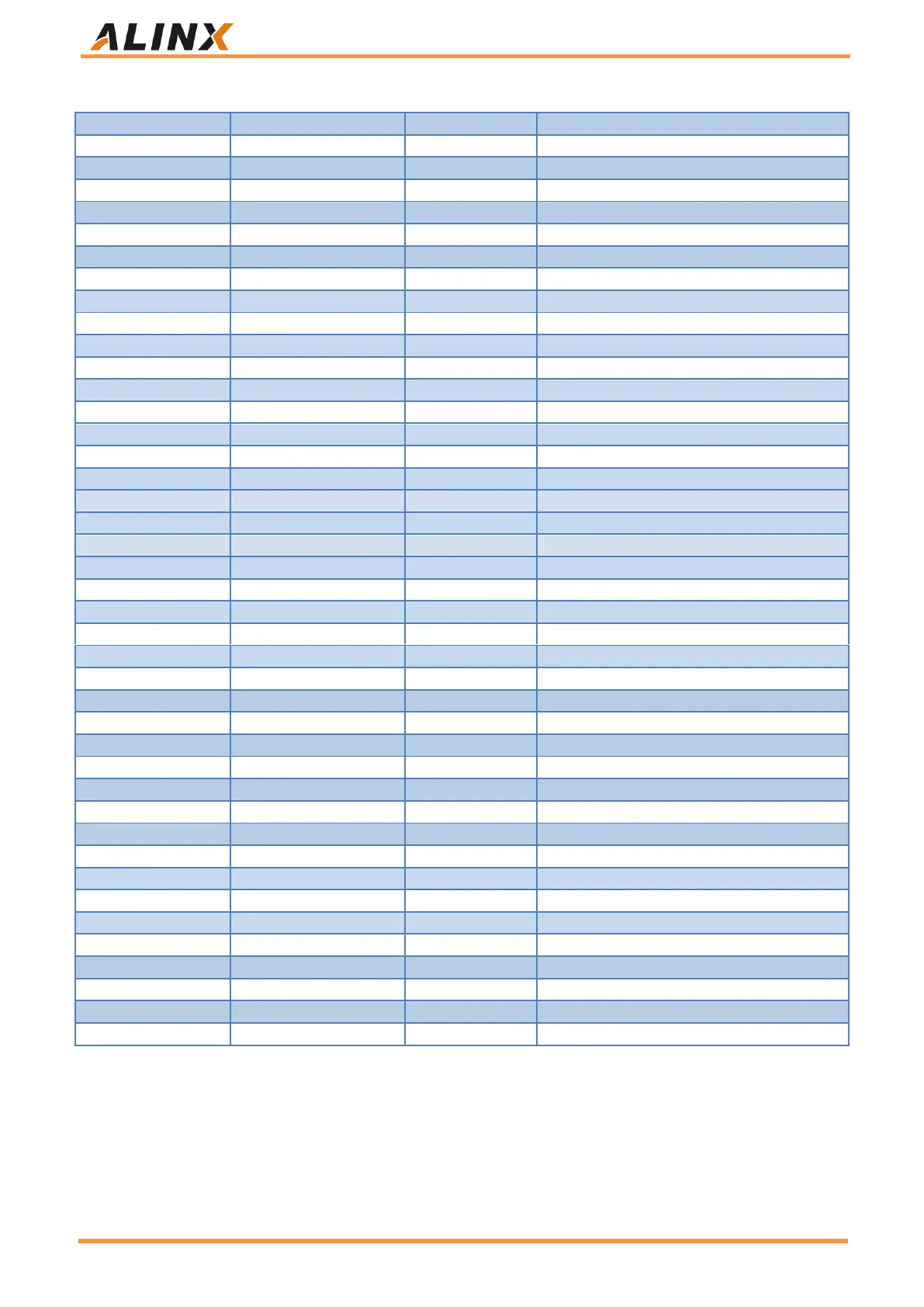

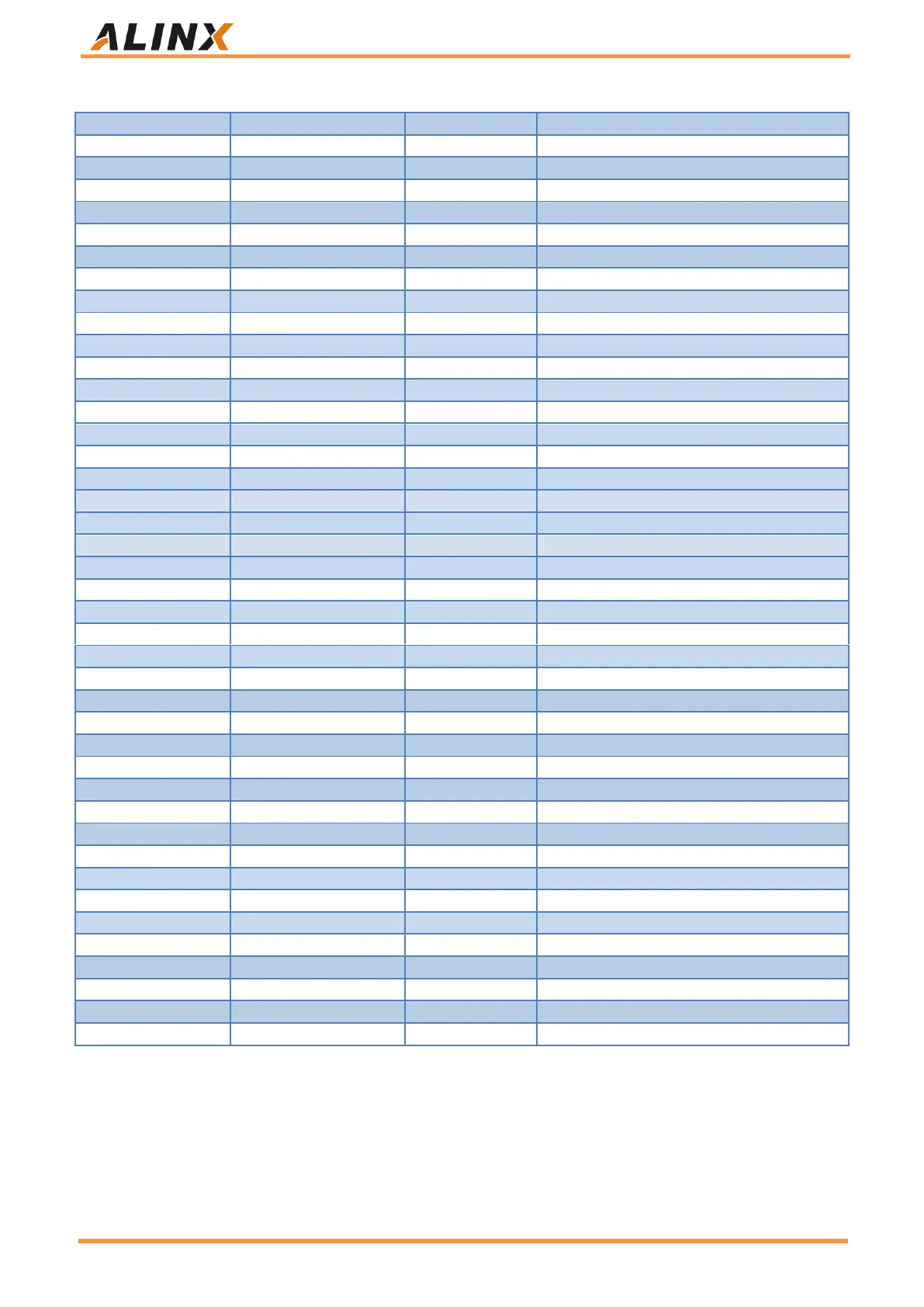

PCIE channel 12 data transmission negative

PCIE Channel 13 Data Sending Positive

PCIE channel 13 data transmission negative

PCIE Channel 14 Data Sending Positive

PCIE channel 14 data transmission negative

PCIE Channel 15 Data Sending Positive

PCIE channel 15 data transmission negative

PCIE channel 0 data sending positive

PCIE channel 0 data transmission negative

PCIE Channel 1 Data Sending Positive

PCIE channel 1 data transmission negative

PCIE Channel 2 Data Sending Positive

PCIE channel 2 data transmission negative

PCIE Channel 3 Data Sending Positive

PCIE channel 3 data transmission negative

PCIE Channel 4 Data Sending Positive

PCIE channel 4 data transmission negative

PCIE Channel 5 Data Sending Positive

PCIE channel 5 data transmission negative

PCIE Channel 6 Data Sending Positive

PCIE channel 6 data transmission negative

PCIE Channel 7 Data Sending Positive

PCIE channel 7 data transmission negative

PCIE Channel 8 Data Sending Positive

PCIE channel 8 data transmission negative

PCIE Channel 9 Data Sending Positive

PCIE channel 9 data transmission negative

PCIE Channel 10 Data Sending Positive

PCIE channel 10 data transmission negative

PCIE Channel 11 Data Sending Positive

PCIE channel 11 data transmission negative

PCIE Channel 12 Data Sending Positive

PCIE channel 12 data transmission negative

PCIE Channel 13 Data Sending Positive

PCIE channel 13 data transmission negative

PCIE Channel 14 Data Sending Positive

PCIE channel 14 data transmission negative

PCIE Channel 15 Data Sending Positive

PCIE channel 15 data transmission negative

PCIE channel reference clock positive

PCIE channel reference clock negative

Table 15: PCIe interface pin assignment

Part 3.3: Gigabit network interface

A JL21221D Ethernet PHY chip is used on the development board to provide network communication services for

users. The Ethernet PHY chip is connected to the IO interface of FPGA. JL21221D chip supports 10/100/1,000 Mbps

Loading...

Loading...