Table 17: Ethernet PHY pin assignment

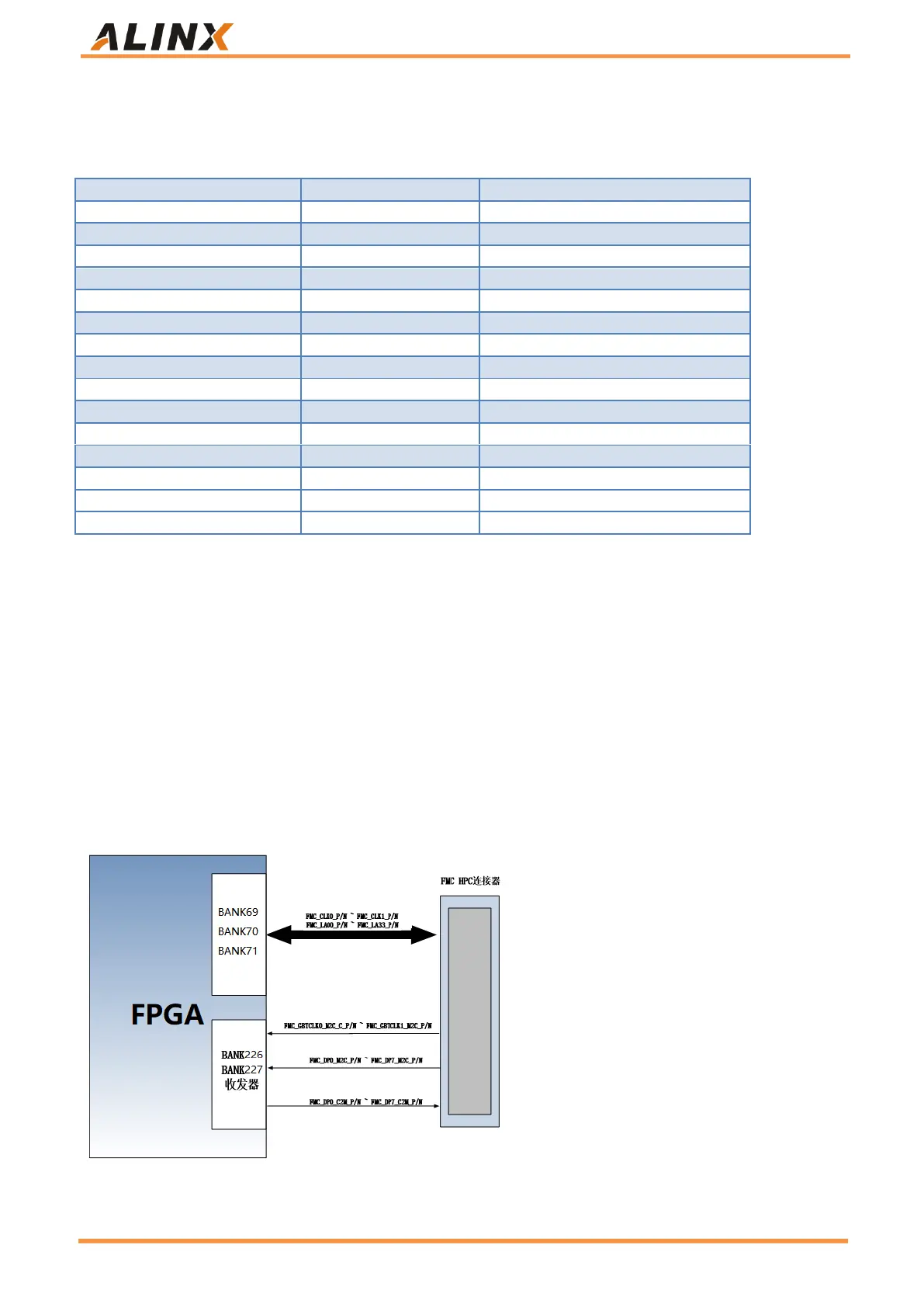

Part 3.4: FMC HPC Interface

The development board is equipped with two FMC HPC expansion ports, namely FMC1 (J12) and FMC2 (J13), which

can be externally connected with XILINX or various FMC modules of Alinx (HDMI input and output module,

binocular camera module, high-speed AD module, etc.).

The FMC1 expansion port includes 34 pairs of LA signal differential pairs, 2 pairs of clock signals and 24 pairs of HA

signals, which are respectively connected to the FPGA chips BANK69, BANK70 and BANK71. The standard level is

1.8V by default. 8 channels of high-speed GTY transceiving signals are connected to the IO of FPGA chips

BANK226 and BANK227.

The schematic diagram of the FPGA and FMC HPC connector is shown in Figure 19:

Figure 19: Connection Schematic Diagram of FMC HPC Interface

Loading...

Loading...