ZYNQ Ultrascale + FPGA Board AXU4EV-E User Manual

Amazon Store: https://www.amazon.com/alinx

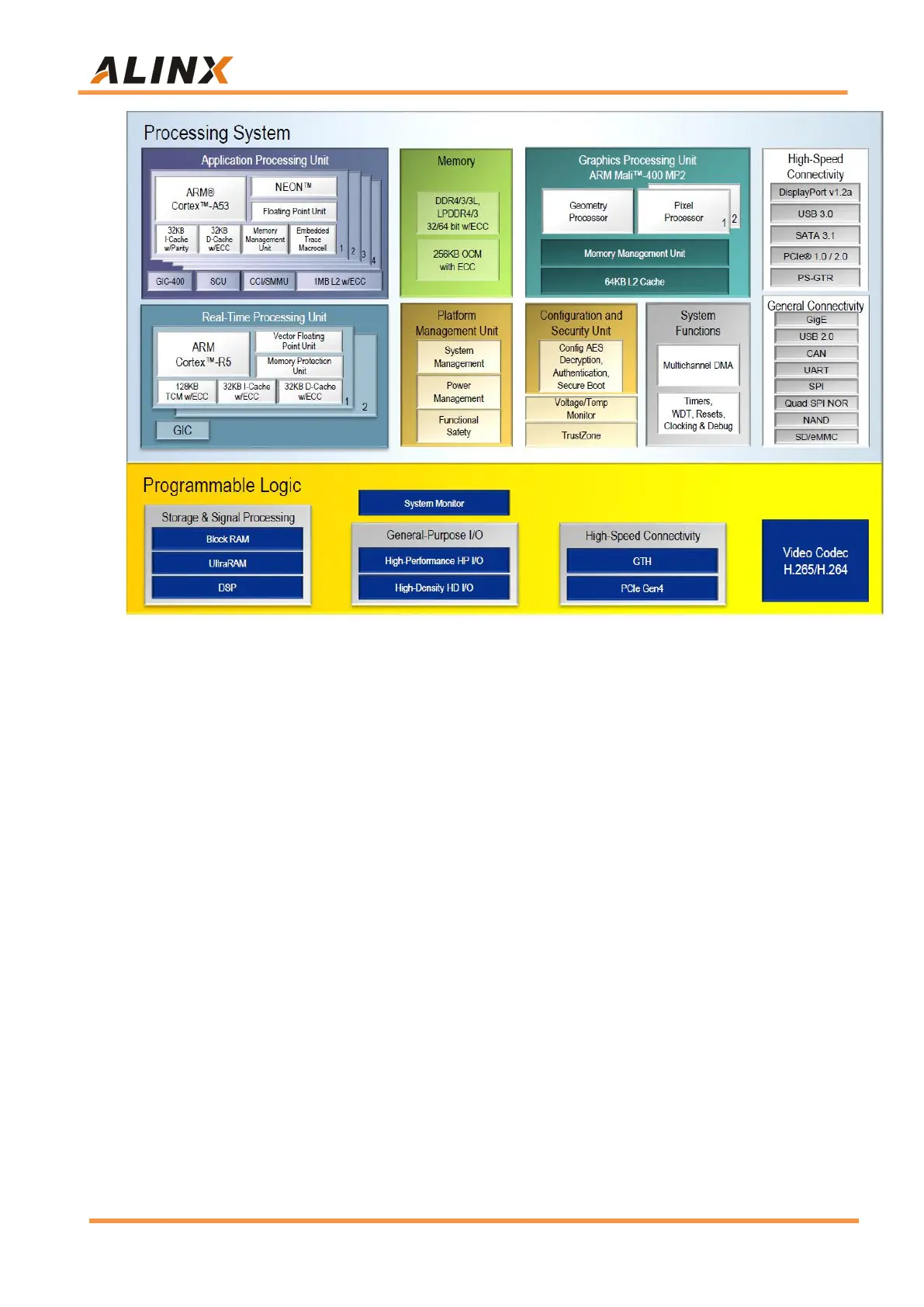

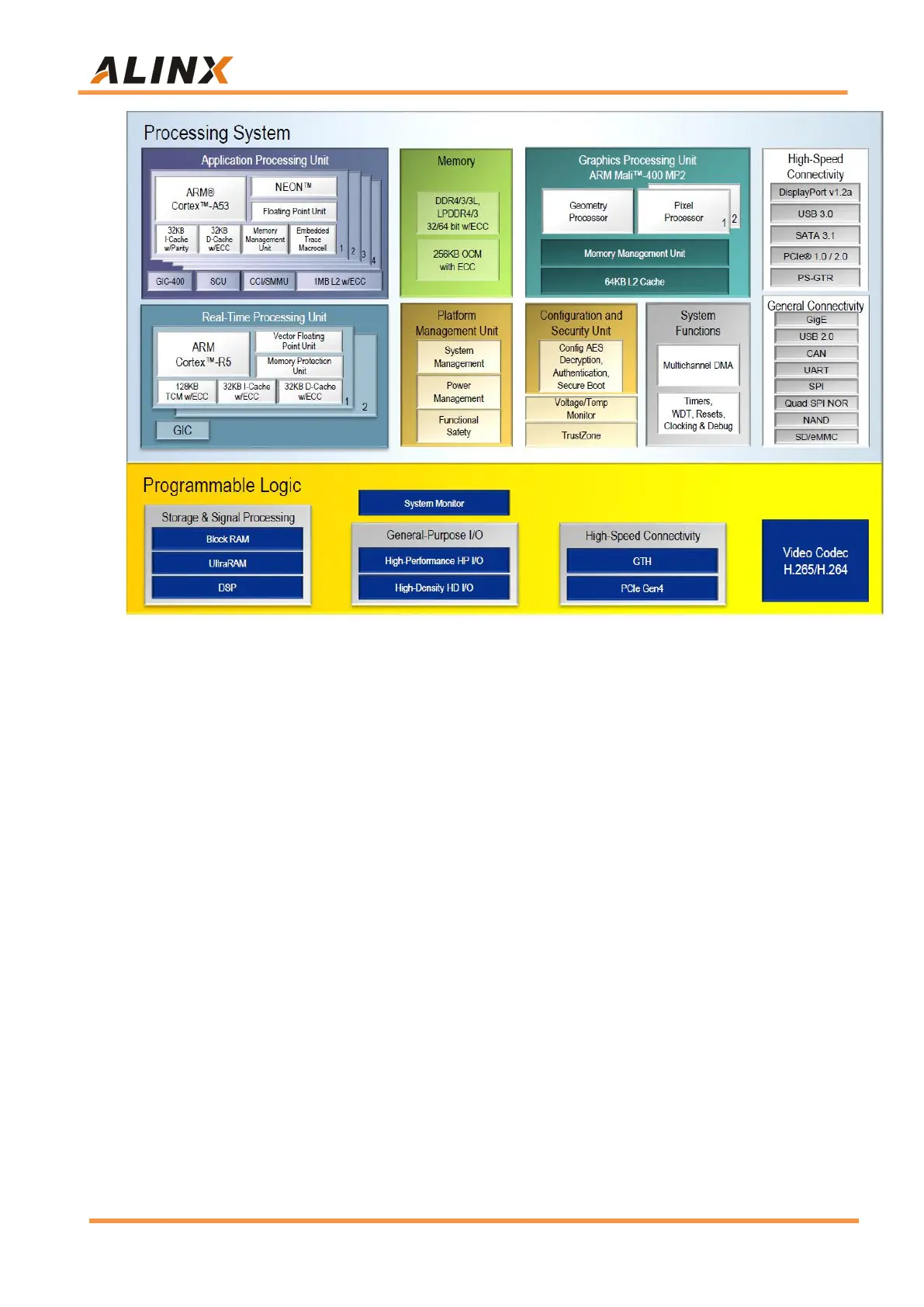

Figure 2-2-1:

Overall Block Diagram of the

ZYNQ ZU4EV

Chip

The main parameters of the PS system part are as follows:

ARM quad-core Cortex ™ -A53 processor, speed up to 1.5GHz, each

CPU 32KB level 1 instruction and data cache, 1MB level 2 cache,

shared by 2 CPUs

ARM dual-core Cortex-R5 processor, speed up to 600MHz, each CPU

32KB level 1 instruction and data cache, and 128K tightly coupled

memory.

Image Video Processor Mali-400 MP2, speed up to 677MHz, 64KB level

2 cache

External storage interface, support 32/64bit DDR4/3/3L, LPDDR4/3

interface

Static storage interface, support NAND, 2xQuad-SPI FLASH.

High-speed connection interface, support PCIe Gen2 x 4, 2 x USB3.0,

Loading...

Loading...