ZYNQ Ultrascale + FPGA Board AXU4EV-E User Manual

Amazon Store: https://www.amazon.com/alinx

The CAN communication pin assignments are as follows:

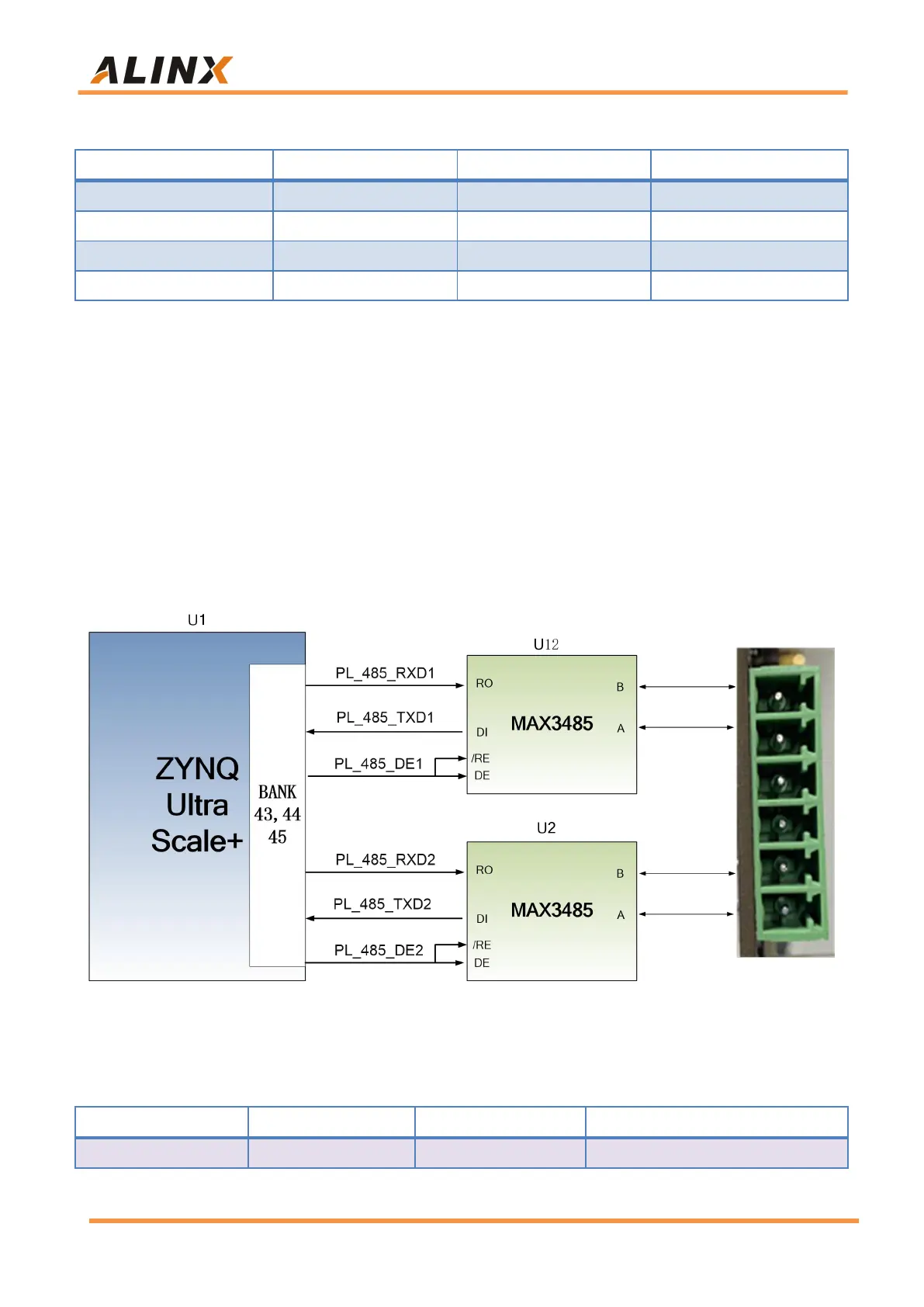

Part 3.10: 485 communication interface

There are two 485 communication interfaces on the AXU4EV-E carrier

board. The 485 communication port 1 is connected to the IO interface of

BANK43~45 on the PL system. The 485 transceiver chip selects the MAX3485

chip from MAXIM for the user's 485 communication service.

Figure 3-3-1 is the connection diagram of the 485 transceiver chip on the

PL side

Figure 3-3-1: 485 Communication on the PL Side

The 485 communication pins are assigned as follows:

The 1

st

Channel 485 Transceiver

Loading...

Loading...