MAX1000 User Guide www.arrow.com

Page | 20 July 2017

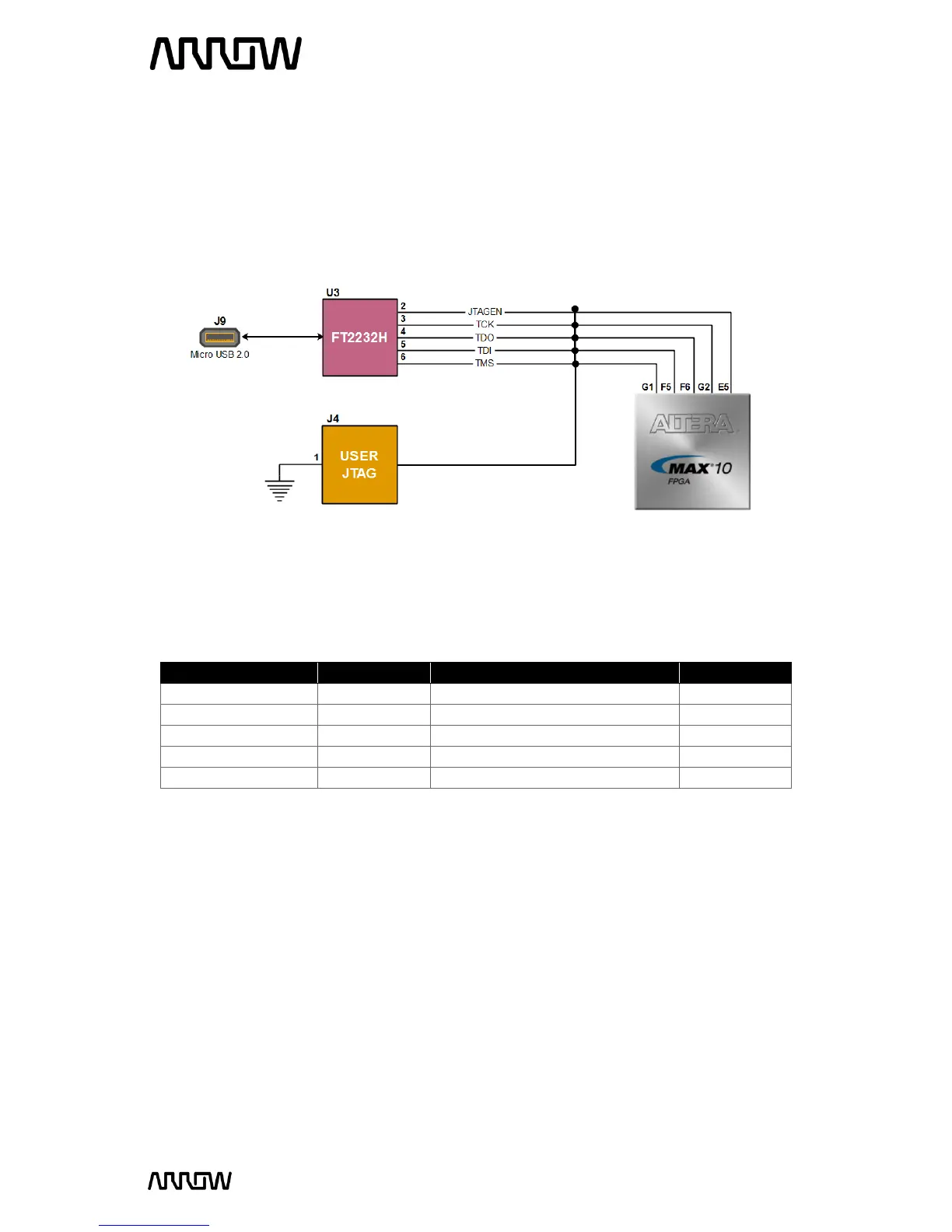

The FPGA device can be configured through JTAG interface on MAX1000, but the JTAG chain must

form a closed loop, which allows Quartus Prime programmer to detect the FPGA device.

MAX1000 offers two ways of configuring your board.

1) Through the on-board Arrow USB Programmer2

2) Pins for connecting user’s preferred JTAG interface

Loading...

Loading...