126

7598H–AVR–07/09

ATtiny25/45/85

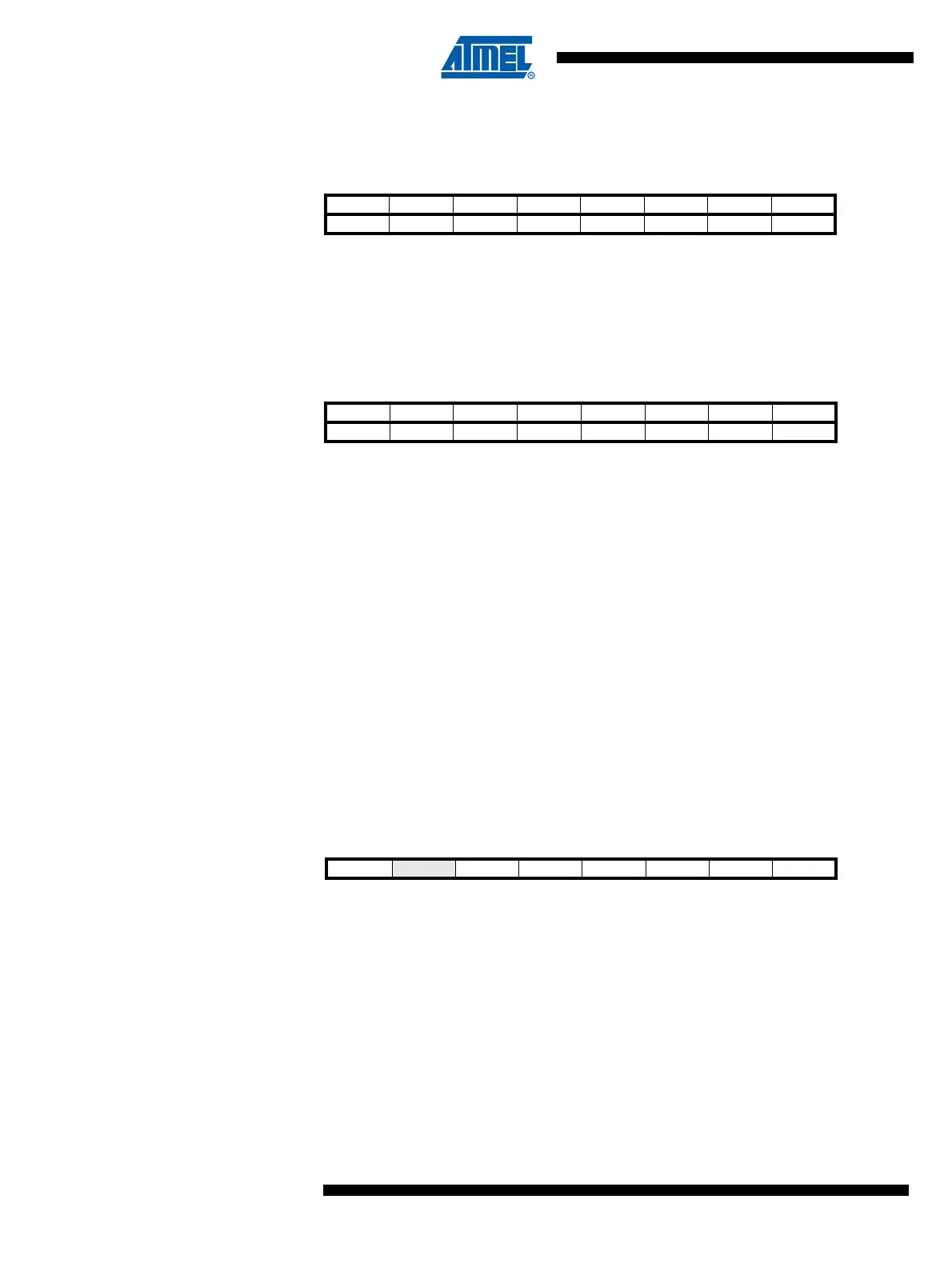

18.7.7 The ADC Data Register – ADCL and ADCH

18.7.7.1 ADLAR = 0

18.7.7.2 ADLAR = 1

When an ADC conversion is complete, the result is found in these two registers.

When ADCL is read, the ADC Data Register is not updated until ADCH is read. Consequently, if

the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read

ADCH. Otherwise, ADCL must be read first, then ADCH.

The ADLAR bit in ADMUX, and the MUXn bits in ADMUX affect the way the result is read from

the registers. If ADLAR is set, the result is left adjusted. If ADLAR is cleared (default), the result

is right adjusted.

• ADC9:0: ADC Conversion Result

These bits represent the result from the conversion, as detailed in “ADC Conversion Result” on

page 121.

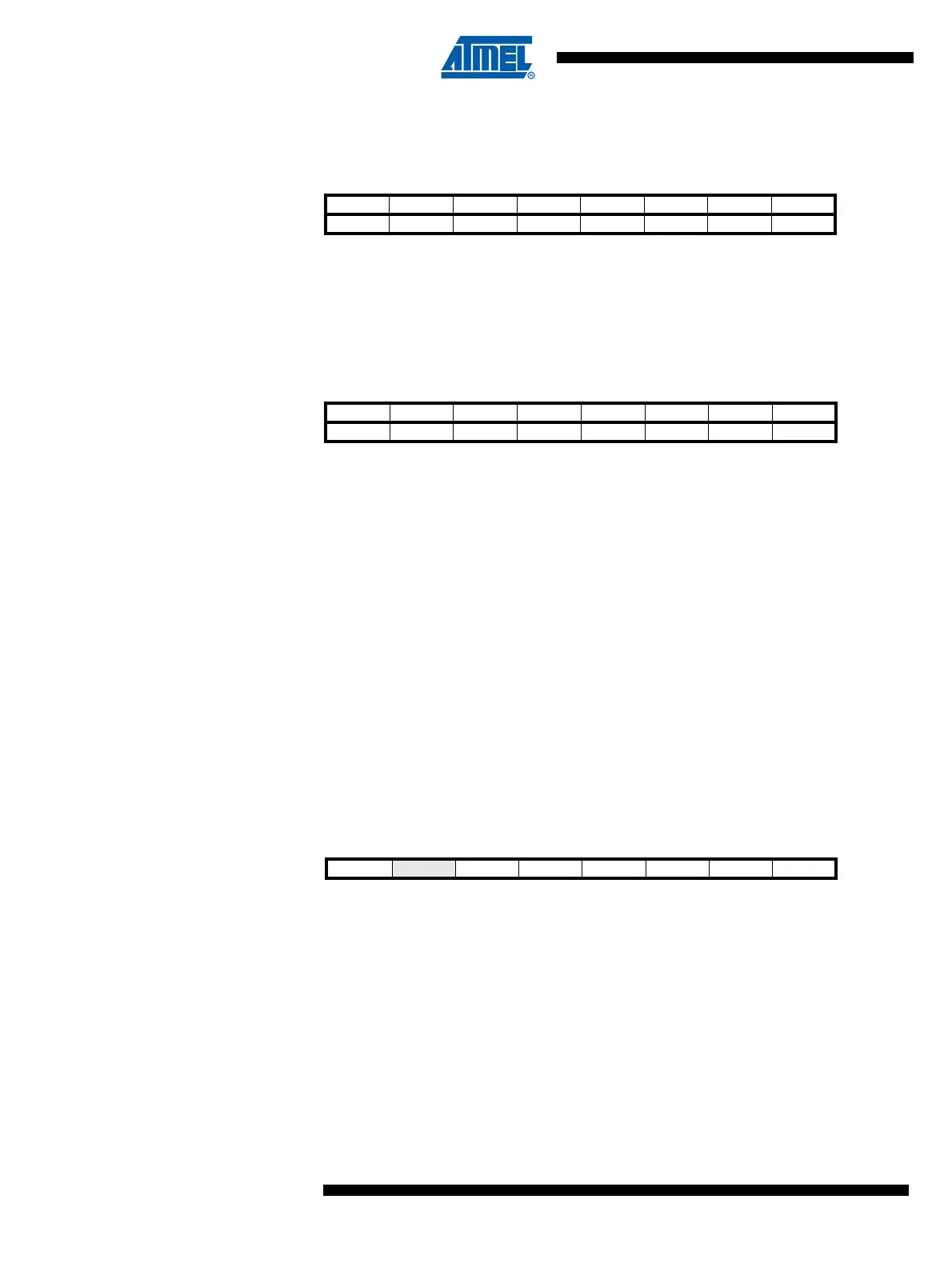

18.7.8 ADC Control and Status Register B – ADCSRB

• Bit 7– BIN: Bipolar Input Mode

The gain stage is working in the unipolar mode as default, but the bipolar mode can be selected

by writing the BIN bit in the ADCSRB register. In the unipolar mode only one-sided conversions

are supported and the voltage on the positive input must always be larger than the voltage on

the negative input. Otherwise the result is saturated to the voltage reference. In the bipolar mode

two-sided conversions are supported and the result is represented in the two’s complement

form. In the unipolar mode the resolution is 10 bits and the bipolar mode the resolution is 9 bits +

1 sign bit.

Bit 151413121110 9 8

– – – – – – ADC9 ADC8 ADCH

ADC7 ADC6 ADC5 ADC4 ADC3 ADC2 ADC1 ADC0 ADCL

76543210

Read/Write RRRRRRRR

RRRRRRRR

Initial Value 0 0 0 0 0 0 0 0

00000000

Bit 151413121110 9 8

ADC9 ADC8 ADC7 ADC6 ADC5 ADC4 ADC3 ADC2 ADCH

ADC1 ADC0 – – – – – – ADCL

76543210

Read/Write RRRRRRRR

RRRRRRRR

Initial Value 0 0 0 0 0 0 0 0

00000000

Bit 76543210

BIN

ACME IPR – – ADTS2 ADTS1 ADTS0 ADCSRB

Read/Write R/W R/W R/W R R R/W R/W R/W

Initial Value00000000

Loading...

Loading...