378

7679H–CAN–08/08

AT90CAN32/64/128

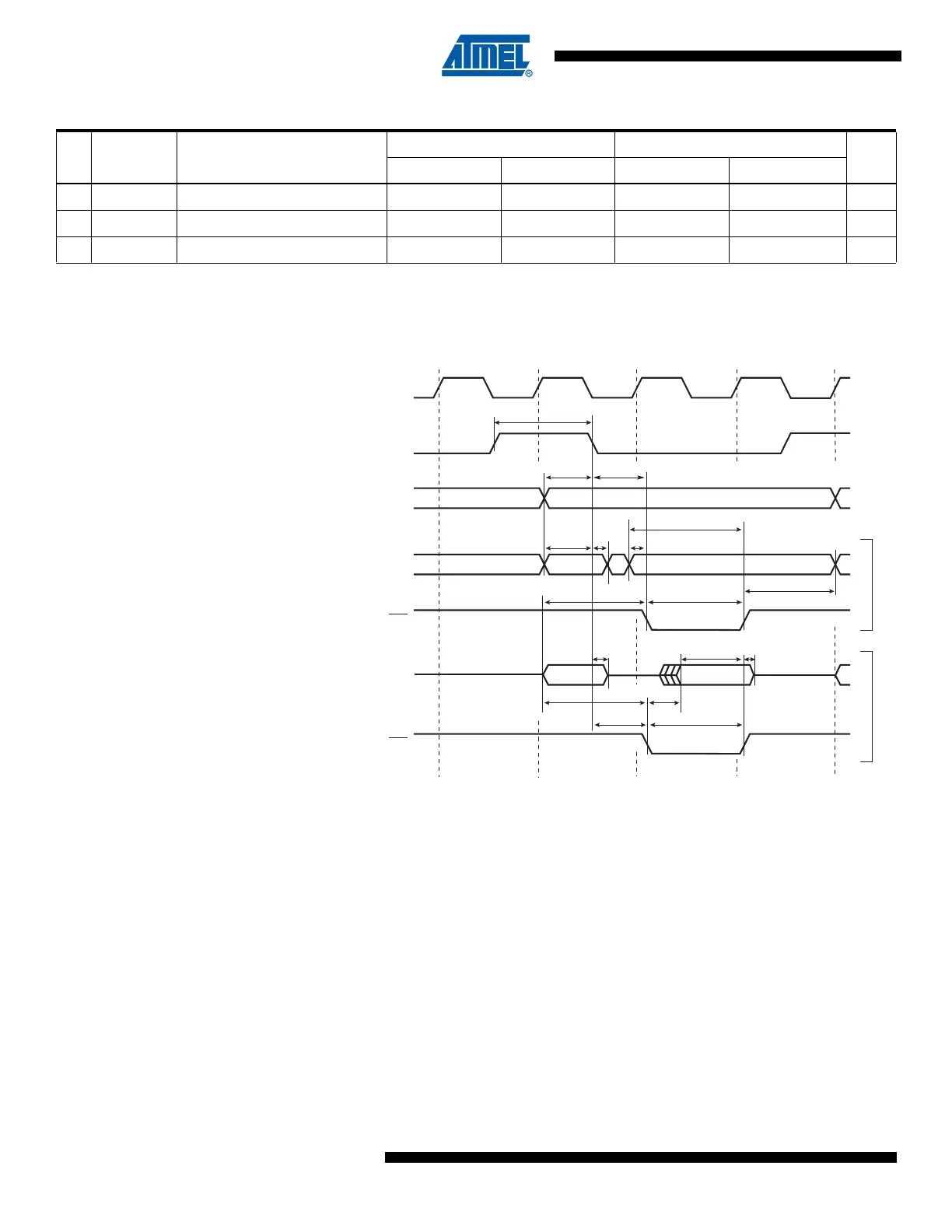

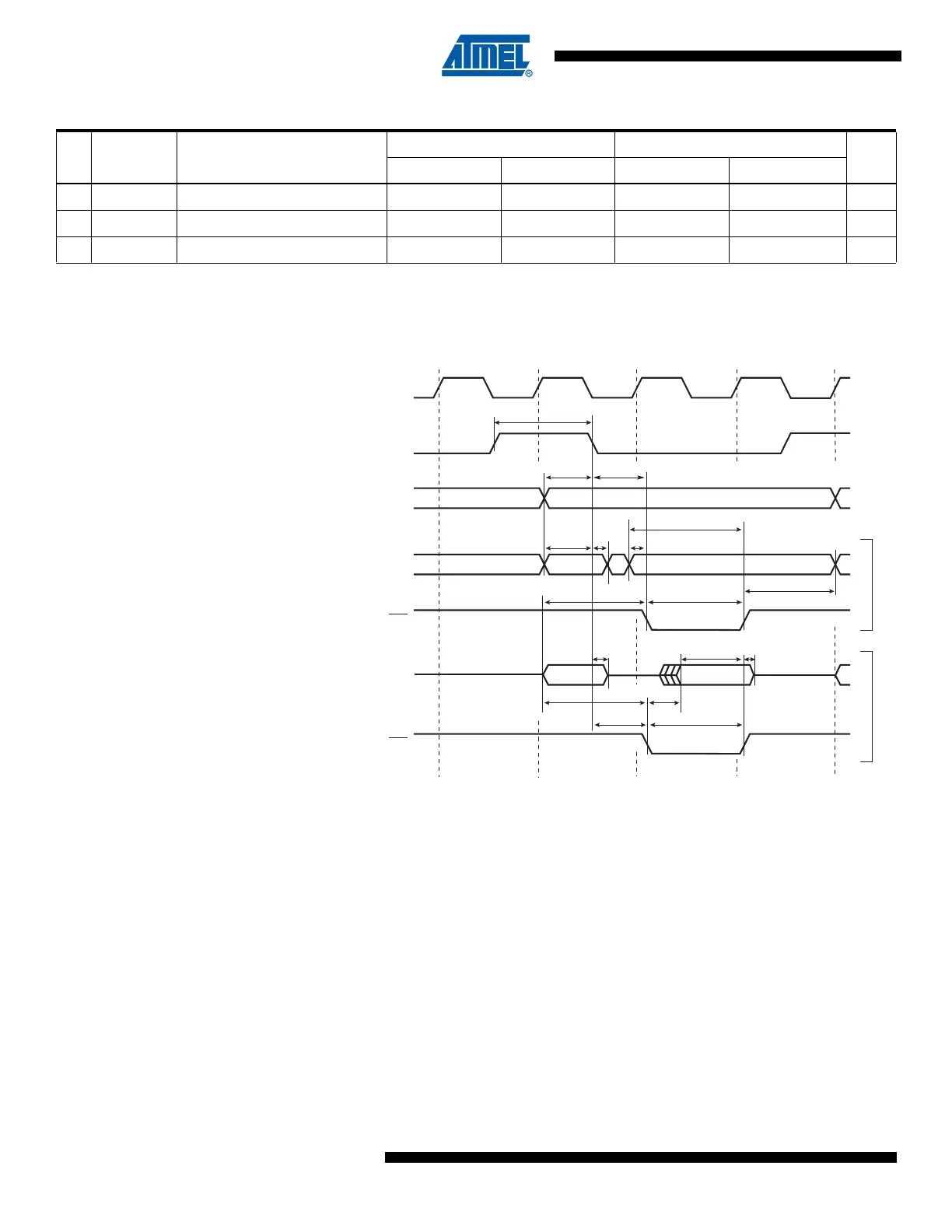

Figure 26-6. External Memory Timing (SRWn1 = 0, SRWn0 = 0)

14 t

WHDX

Data Hold After WR High 485 2.0 t

CLCL

– 15 ns

15 t

DVWH

Data Valid to WR High 750 3.0 t

CLCL

ns

16 t

WLWH

WR Pulse Width 735 3.0 t

CLCL

– 15 ns

Table 26-14. External Data Memory Characteristics, V

CC

= 2.7 - 5.5 Volts, SRWn1 = 1, SRWn0 = 1 (Continued)

Symbol Parameter

4 MHz Oscillator Variable Oscillator

Unit

Min. Max. Min. Max.

ALE

T1 T2 T3

Write

Read

WR

T4

A15:8

AddressPrev. addr.

DA7:0

Address DataPrev. data XX

RD

DA7:0 (XMBK = 0)

DataAddress

System Clock (CLK

CPU

)

1

4

2

7

6

3a

3b

5

8 12

16

13

10

11

14

15

9

Loading...

Loading...