45

7679H–CAN–08/08

AT90CAN32/64/128

“0011”, giving a division factor of 8 at start up. This feature should be used if the selected clock

source has a higher frequency than the maximum frequency of the device at the present operat-

ing conditions. Note that any value can be written to the CLKPS bits regardless of the CKDIV8

Fuse setting. The Application software must ensure that a sufficient division factor is chosen if

the selected clock source has a higher frequency than the maximum frequency of the device at

the present operating conditions. The device is shipped with the CKDIV8 Fuse programmed.

Note: The frequency of the asynchronous clock must be lower than 1/4th of the frequency of the scaled

down Source clock. Otherwise, interrupts may be lost, and accessing the Timer/Counter2 regis-

ters may fail.

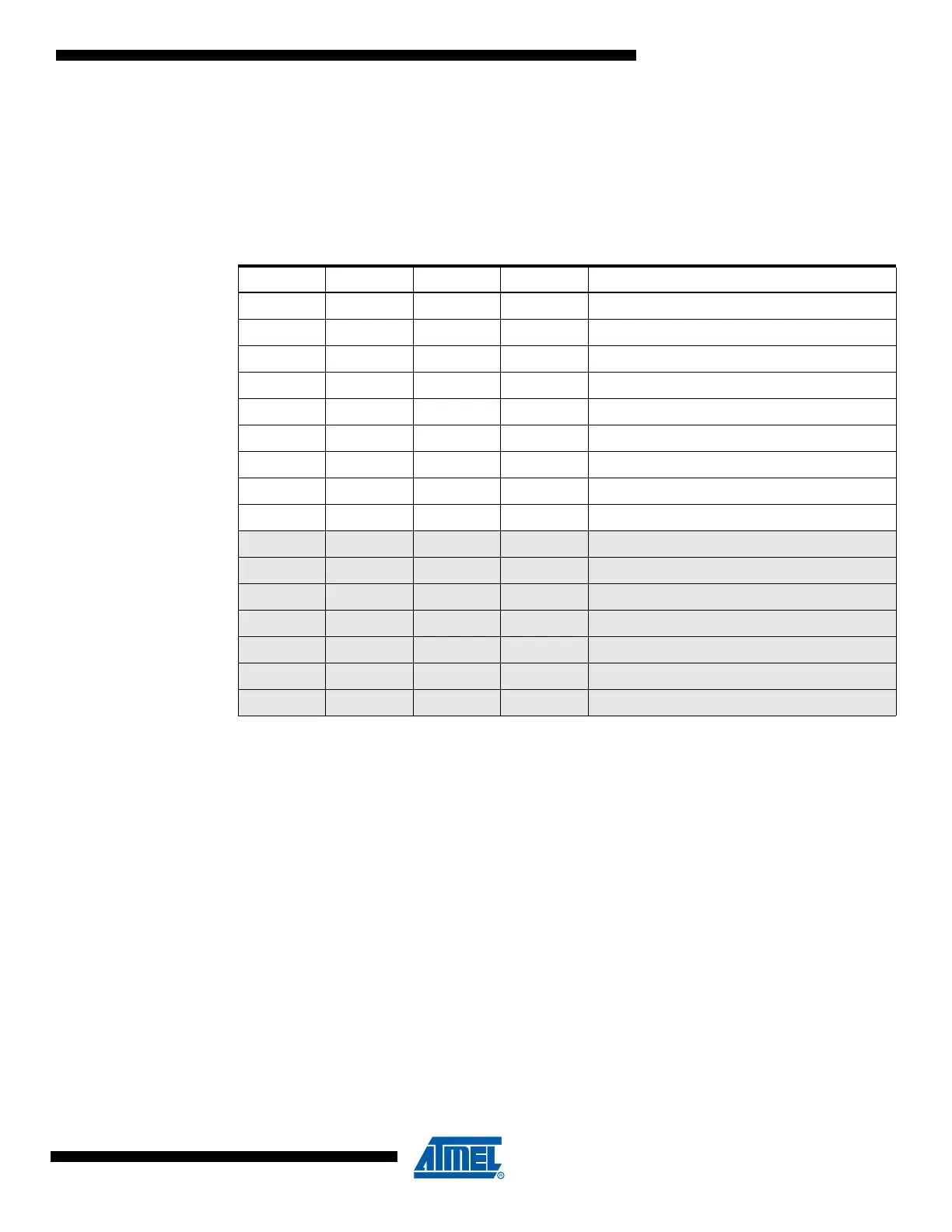

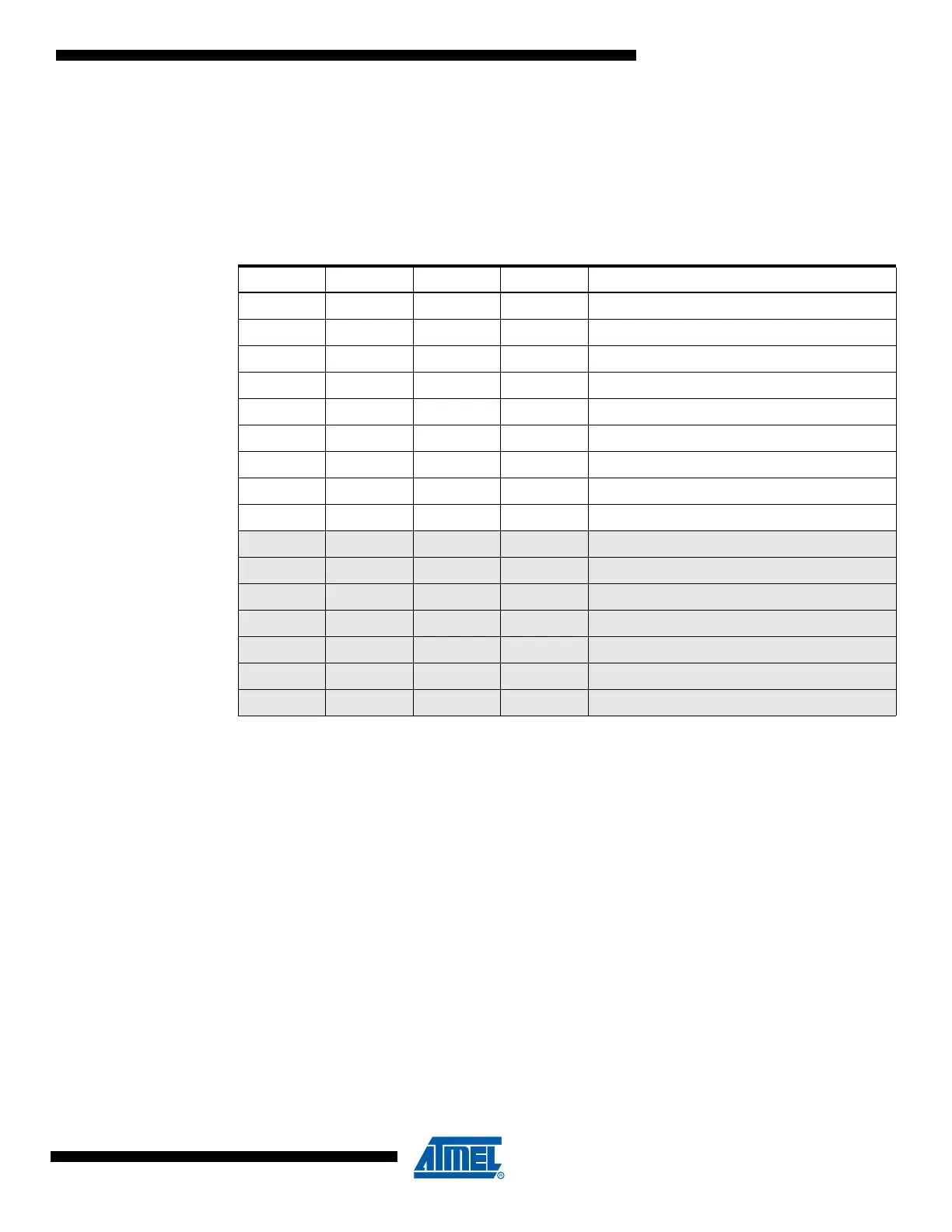

Table 5-12. Clock Prescaler Select

CLKPS3 CLKPS2 CLKPS1 CLKPS0 Clock Division Factor

00001

00012

00104

00118

010016

010132

011064

0111128

1000256

1 0 0 1 Reserved

1 0 1 0 Reserved

1 0 1 1 Reserved

1 1 0 0 Reserved

1 1 0 1 Reserved

1 1 1 0 Reserved

1 1 1 1 Reserved

Loading...

Loading...