85

7679H–CAN–08/08

AT90CAN32/64/128

Note: 1. AIN0D and AIN1D is described in “Digital Input Disable Register 1 – DIDR1” on page 272.

9.3.7 Alternate Functions of Port F

The Port F has an alternate function as analog input for the ADC as shown in Table 9-18. If

some Port F pins are configured as outputs, it is essential that these do not switch when a con-

version is in progress. This might corrupt the result of the conversion. If the JTAG interface is

enabled, the pull-up resistors on pins PF7 (TDI), PF5 (TMS) and PF4 (TCK) will be activated

even if a reset occurs.

The alternate pin configuration is as follows:

• TDI, ADC7 – Port F, Bit 7

ADC7, Analog to Digital Converter, input channel 7

.

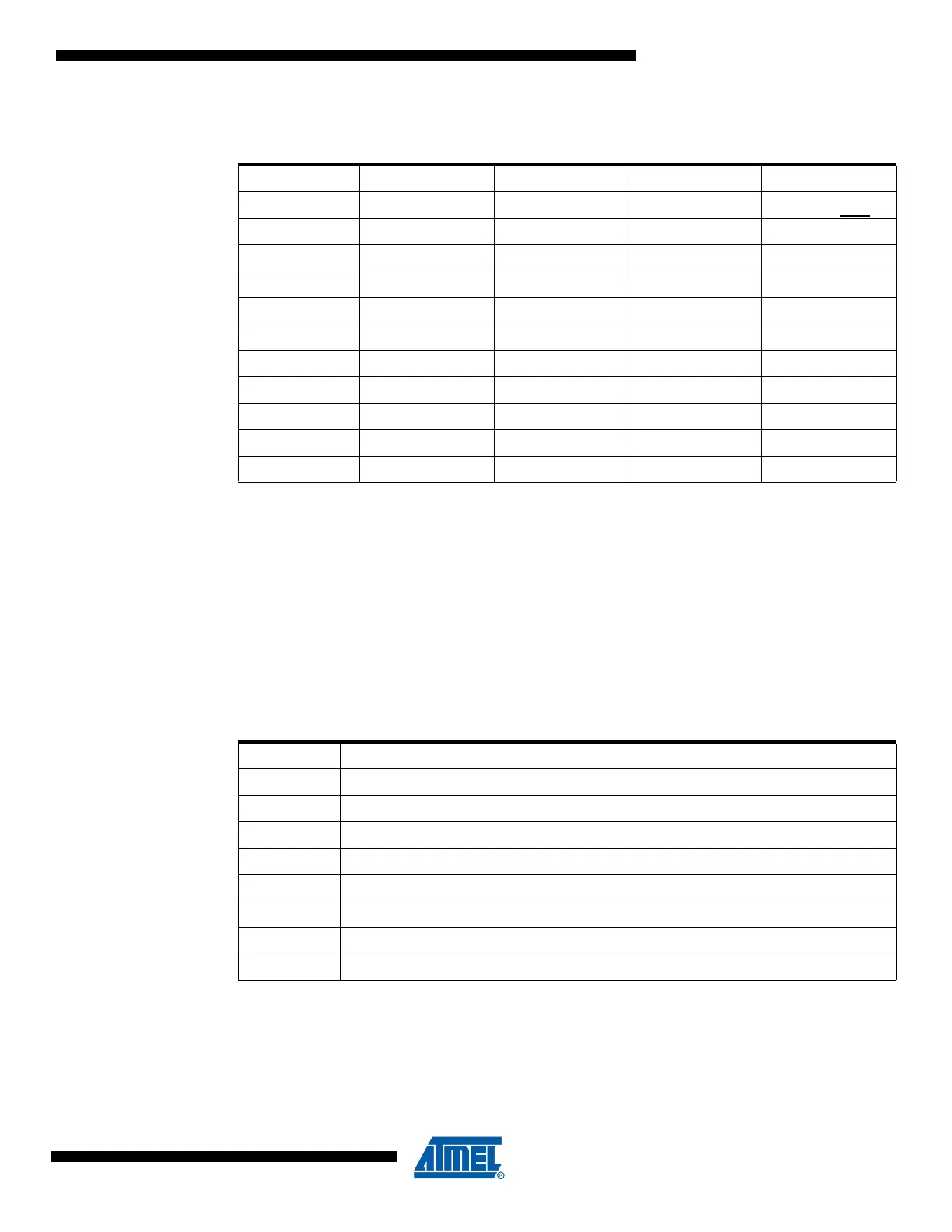

Table 9-17. Overriding Signals for Alternate Functions in PE3..PE0

Signal Name PE3/AIN1/OC3A PE2/AIN0/XCK0 PE1/PDO/TXD0 PE0/PDI/RXD0

PUOE 0 0 TXEN0 RXEN0

PUOV000PORTE0 • PUD

DDOE 0 0 TXEN0 RXEN0

DDOV0010

PVOE OC3A ENABLE UMSEL0 TXEN0 0

PVOV OC3A XCK0 OUTPUT TXD0 0

PTOE0000

DIEOE AIN1D

(1)

AIN0D

(1)

00

DIEOV0000

DI 0 XCK0 INPUT – RXD0

AIO AIN1 INPUT AIN0 INPUT – –

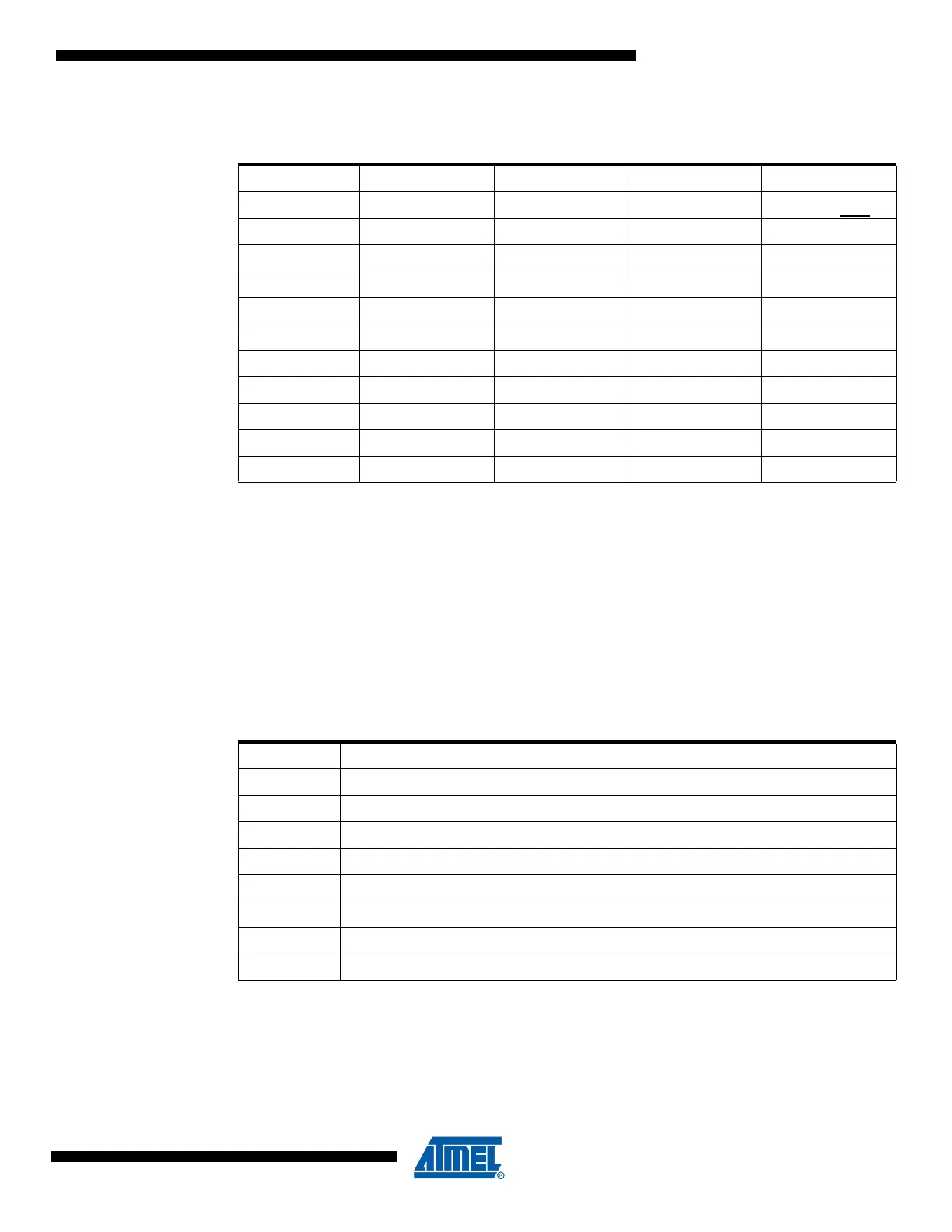

Table 9-18. Port F Pins Alternate Functions

Port Pin Alternate Function

PF7 ADC7/TDI (ADC input channel 7 or JTAG Data Input)

PF6 ADC6/TDO (ADC input channel 6 or JTAG Data Output)

PF5 ADC5/TMS (ADC input channel 5 or JTAG mode Select)

PF4 ADC4/TCK (ADC input channel 4 or JTAG ClocK)

PF3 ADC3 (ADC input channel 3)

PF2 ADC2 (ADC input channel 2)

PF1 ADC1 (ADC input channel 1)

PF0 ADC0 (ADC input channel 0)

Loading...

Loading...