Digital Power Meter 66203/66204 User’s Manual

6-4

6.2.3 Questionable Status

■ The Questionable Status registers inform you one or more questionable status

conditions which indicate certain errors or faults have occurred to at least one channel.

Table 6-2 lists the questionable status conditions that are applied to the electronic load.

These conditions are sa

me as the channel status conditions. Refer to Table 6-1 for a

complete description

.

■ When a corresponding bit of Questionable Status Condition register is set, it indicates

the condition is true.

■ Program the PTR/NTR filter to select the way of condition transition in the Questionable

Status Condition register that will be set in the Event registers.

■ Reading the Questionable Status Event register will reset it to zero.

■ The Questionable status Enable register can be programmed to specify the

questionable status event bit that is logically ORed to become Bit 3 (QUES bit) in the

Status Byte register.

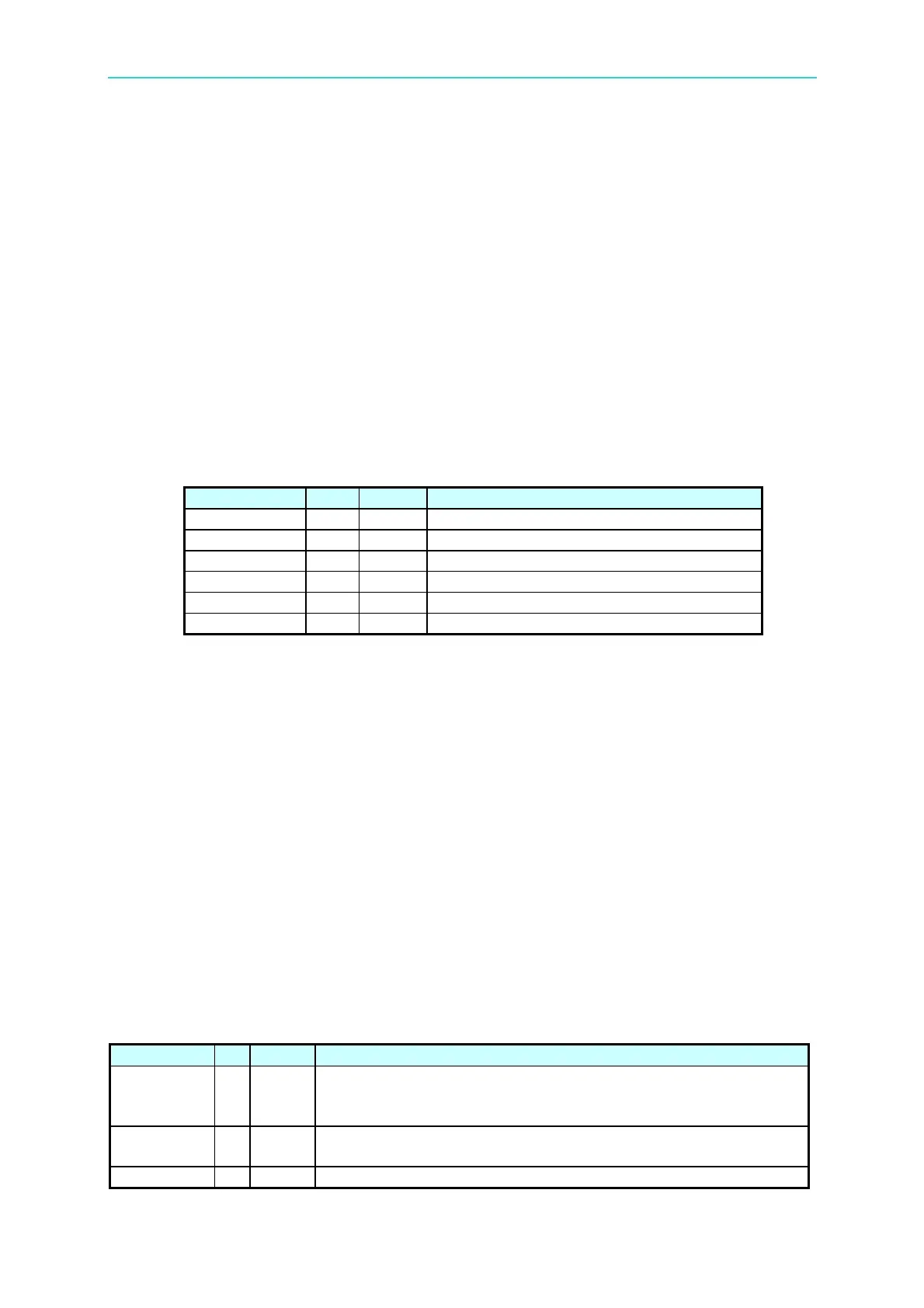

Table 6-2 Bit Description of Questionable Status

Mnemonic Bit Value Meaning

OVR

0 1 Over voltage range.

OCR

1 2 Over current range.

OCP

2 4 Over current.

RCE

3 8 Integration range changed error.

RCE

4 16 Inrush range changed error.

RCE

5 32 Energy range changed error.

6.2.4 Output Queue

■ The Output Queue stores output messages until they are read from the electronic load.

■ The Output Queue stores messages sequentially on a FIFO (First-In, First-Out) basis.

■ It sets to 4 (MAV bit) in the Status Byte register when there are data in the queue.

6.2.5 Standard Event Status

■ All programming errors that have occurred will set one or more error bits in the Standard

Event Status register. Table 6-3 describes the standard events that apply to the

electronic lo

ad.

■ Reading the Standard Event Status register will reset it to zero.

■ The Standard Event Enable register can be programmed to specify the standard event

bit that is logically ORed to become Bit 5 (ESB bit) in the Status Byte register.

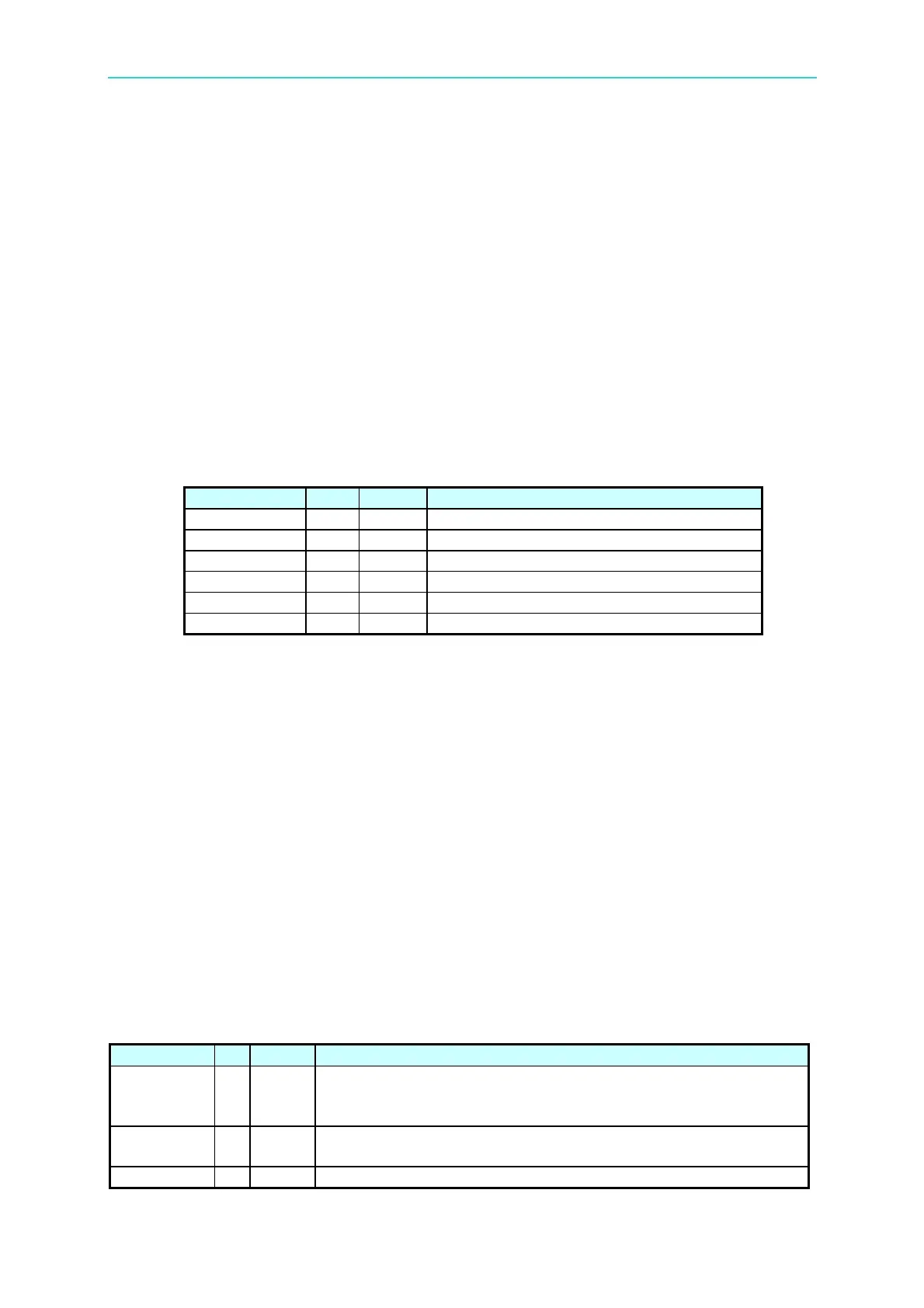

Table 6-3 Bit Description of Standard Event Status

Mnemonic Bit Value Meaning

OPC

0 1 Operation Complete. This event bit generated is responding to

the *OPC command. It indicates that the device has completed

all of the selected pending operations.

QYE

2 4 Query Error. The output queue was read when no data were

present or the data in the queue were lost.

DDE

3 8 Device Dependent Error. Memory was lost, or self-test failed.

Loading...

Loading...