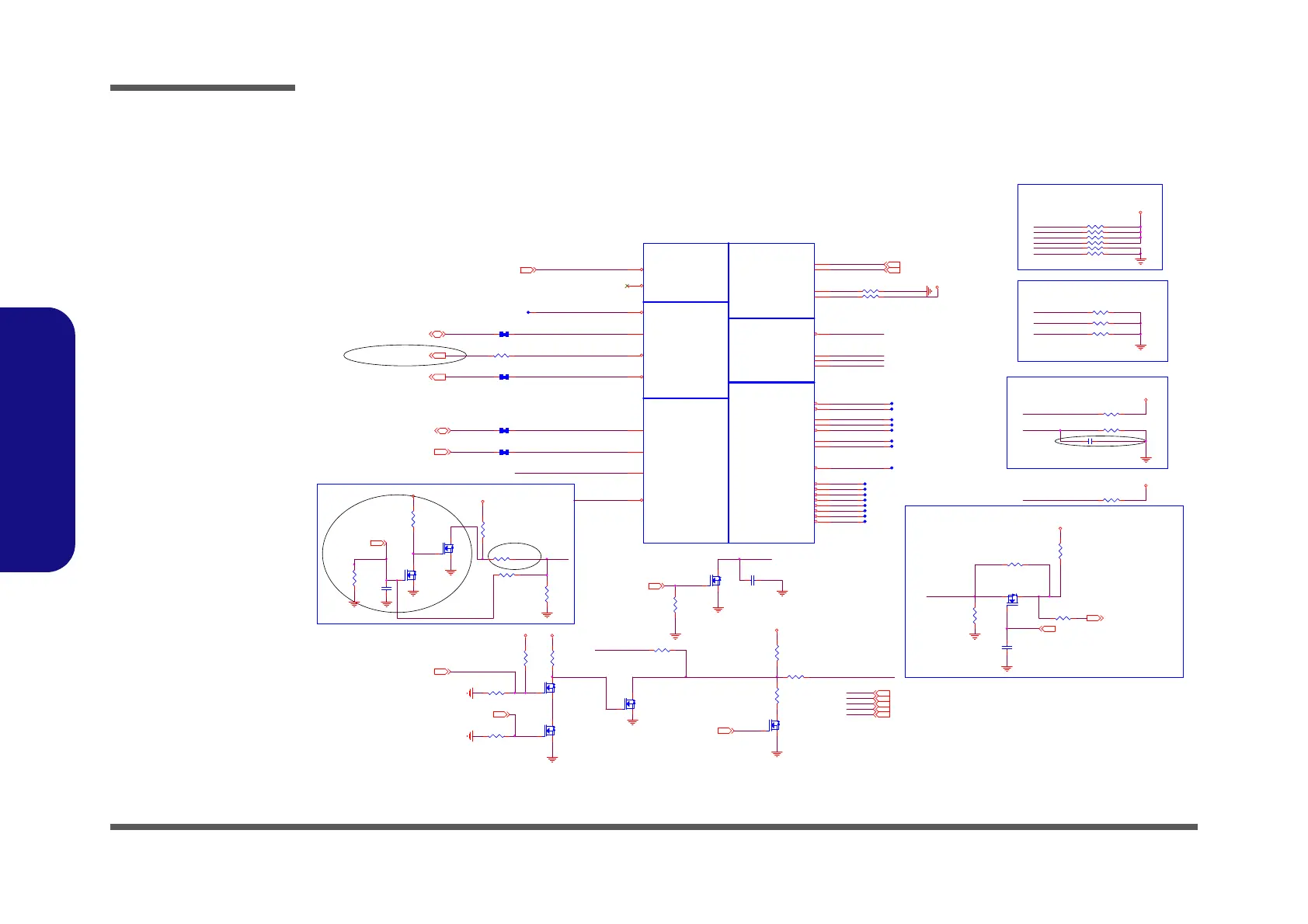

R4910K_1%_04

C494

*47n_50V_04

R409 140_1%_04

3.3VS

R331

4.99K_1%_04

R67 51_04

R4262_04

R333 25. 5_1%_04

D02A

R329

1K_04

R51 *10mil_short

R308 51_04

R82 51_04

R52 56_04

R41 *10mil_short

R309 51_04

R334 200_1%_04

R302 *10m il_short

Q24

RJU003N03T106

G

DS

R84 *51_04

R327 *0_04

R50 *10mil_short

R76 51_04

1.5V

1.05VS_VTT 3,6,24,25,26,40,43

1.05VS_VTT

1.05VS_VTT

3.3V 3,9, 14,15,19,20, 21,23,24,25, 26,28,29,30,32,35,36,37, 39,40,41,42

DRAMRST_CNTRL 9,20

DDR3_DRAMRST# 10,11,12,13

1.5V 9,10, 11,12,13,26, 30,37,39,41

CLK_EXP_N 20

CLK_EXP_P 20

1.5VS_CPU 7,39

H_PROCHOT#43

CPUDRAMRST#

H_TH RMTRI P#24

H_PECI24,34

H_PM_SYNC21

H_CPUPWRGD24

SUSB25,39,40,41,42

H_CPUPWRGD_R

R127 130_04

XD P _D B R _R

BUF _CPU_RST#

R132

0_04

3.3VS

R3011K_04

XD P _D B R _R

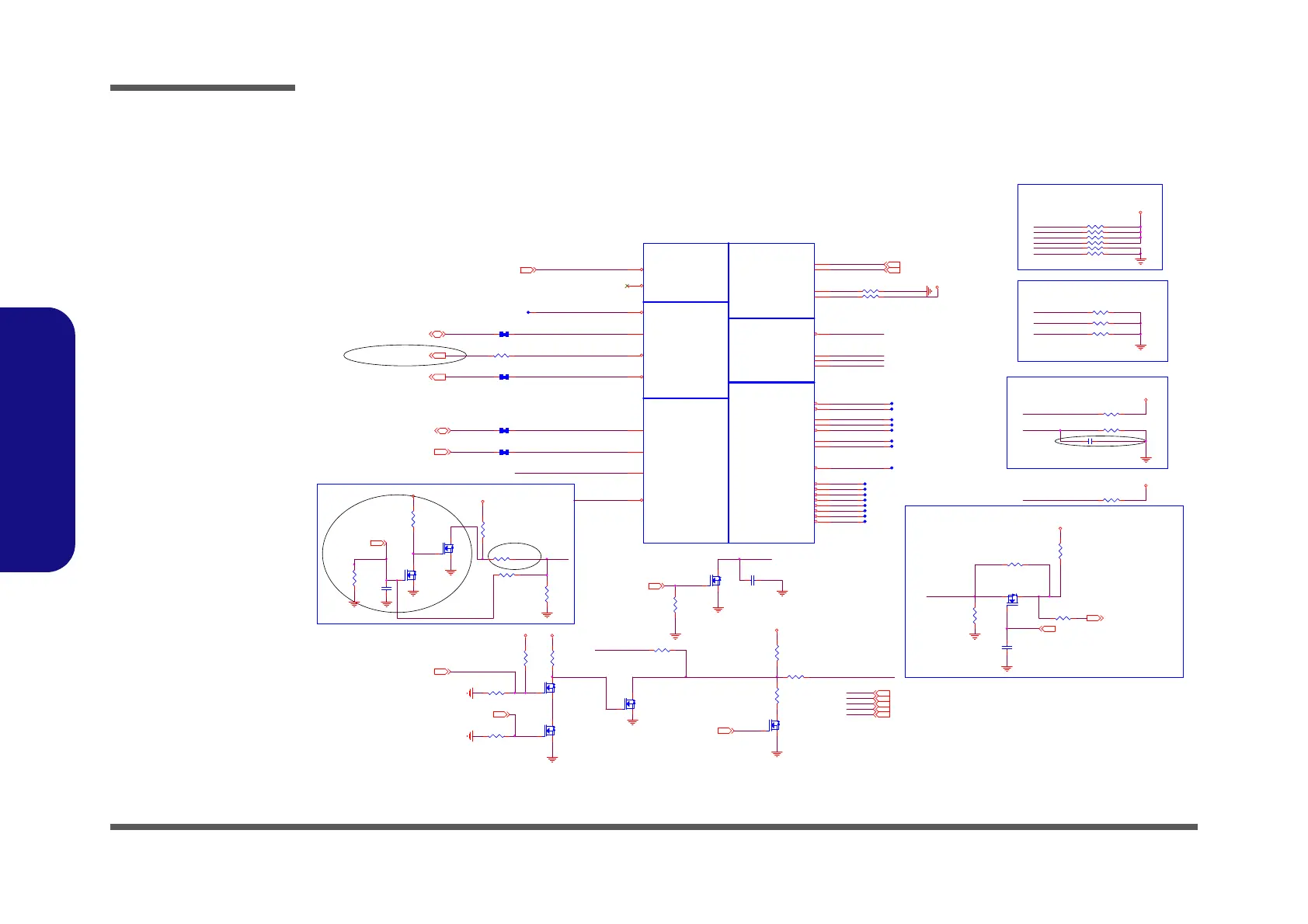

CLOCKS

MISCTHERMALPWR MANAGEMENT

DDR3

MISC

JTAG & BPM

U32B

PZ98927-3641-01F

SM_RCOMP[1]

A5

SM_RCOMP[2]

A4

SM_DRAMRST#

R8

SM_RCOMP[0]

AK1

BCLK#

A27

BCLK

A28

DPLL_REF_SSCLK#

A15

DPLL_REF_SSCL K

A16

CATERR#

AL33

PECI

AN33

PROCHOT#

AL32

THERMTRI P#

AN32

SM_DR AMPWROK

V8

RESET#

AR33

PRDY #

AP29

PREQ#

AP27

TC K

AR26

TMS

AR27

TRS T#

AP30

TDI

AR28

TDO

AP26

DBR#

AL35

BPM#[0]

AT28

BPM#[1]

AR29

BPM#[2]

AR30

BPM#[3]

AT30

BPM#[4]

AP32

BPM#[5]

AR31

BPM#[6]

AT31

BPM#[7]

AR32

PM_SY NC

AM34

SKTOCC#

AN34

SNB_IVB#

C26

UNCOREPWRGOOD

AP33

R97

10K_04

3.3VS 10,11,12,13,14, 15,16,17,18, 19,20,21,23, 24,25,26,29,30,32,33,34,35,36,39,40,43,58

VDDPWR GOOD_R

SM_RC OMP_2

SM_RC OMP_1

SM_RC OMP_0

PLT_RST#14,23,58

XD P _T RS T #

XD P _T CL K

VDDPWRGOOD_R

H_PROCHOT#_D

H_CATERR#

XD P _T MS

CPUDRAMRST#

XD P _P R E Q#

XD P _T DI _ R

XD P _T DO _ R

R328 1K_04

S3 circuit:- DRAM_RST# to memory

should be high during S3

R118

*10K_04

3.3V

R107

*200_04

R115

*100K_04

PM_DRAM_PWRGD21

PM_DRAM_PWRGD

Q8

*MTN7002ZHS3

G

DS

Q10

*MTN7002ZHS3

G

DS

Q11

*MTN7002ZHS3

G

DS

+1.5S_CPU _PWRGD39,41

R103

*100K_04

XD P _P R D Y #

3.3V

H_PROCHOT#

C82 68P_50V_04

C449 0.1u_16V_Y 5V_04

R325 1K_04

1.05VS_VTT

H_CPUPWRGD_R

R117

200_04

1.5VS_CPU

Add to connect to EC

DDR3 Compensation Signals

XD P _T D O_ R

TRACE WIDTH 10MIL, LENGTH <500MILS

PU/PD for JTAG signals

XD P _T MS

BUF _CPU_RST#

Processor Pullups/Pull downs

XD P _T R ST #

H_PROCHOT#

XD P _T C LK

XD P _P R E Q#

XD P _T D I _R

SM_RCOMP_1

SM_RCOMP_0

SM_RCOMP_2

H_PROCHOT#_EC34

R34

100K_04

C60

68P_50V_04

R48

*750_1%_04

R38 *1.5K_1%_04

Q37

MTN7002ZHS3

G

DS

DRAMPWRGD_CPU

Q38

MTN7002ZHS3

G

DS

1.05VS_VTT

R322 1K_04

Q13

*MTN7002ZHS3

G

DS

Sandy Bridge Processor 2/7 ( CLK,MISC,JTAG )

R128

*39_04

R511

100K_04

BSS138 ( VGS 1.5V )

PROC _SEL ET

R40 43.2_1%_04

Buffered reset to CPU

PM_DRAM_PWRGD

Q6

MTN7002ZHS3

G

DS

PRO C_SELET24

R39

75_04

Loading...

Loading...