Chapter 6 Function Introduction Shenzhen Hpmont Technology Co., Ltd

―64― HD30 Series Inverters User Manual

No. Name Description Range

factory setting

F04.09 Sampling cycle (T) 0.01

50.00s

0.10

F04.04, F04.05 and F04.07 define the process PID parameters.

F04.06 defines the process PID integral upper limit.

F04.08 defines the process PID differential amplitude limit value.

F04.09 defines the sampling cycle of feedback value and the PID regulator calculates once in each

sampling cycle.

• When F04.07 = 0, the differential is disabled.

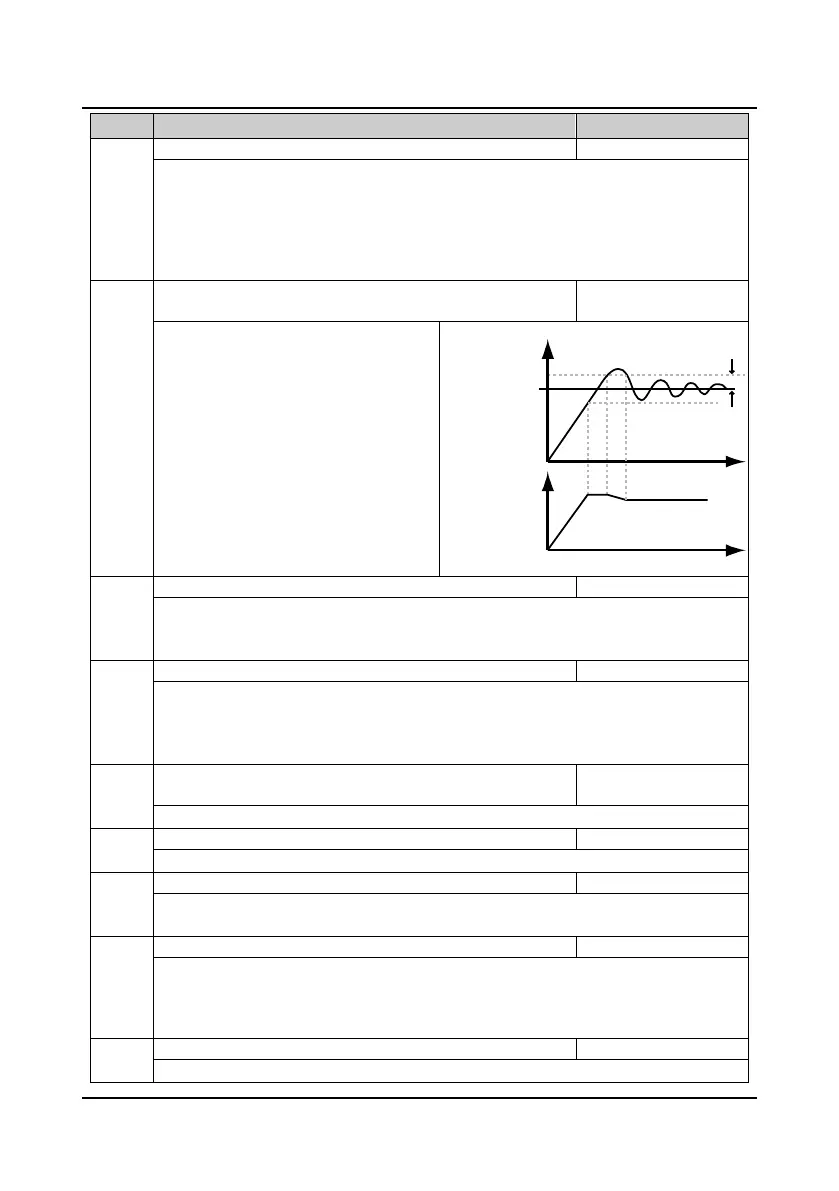

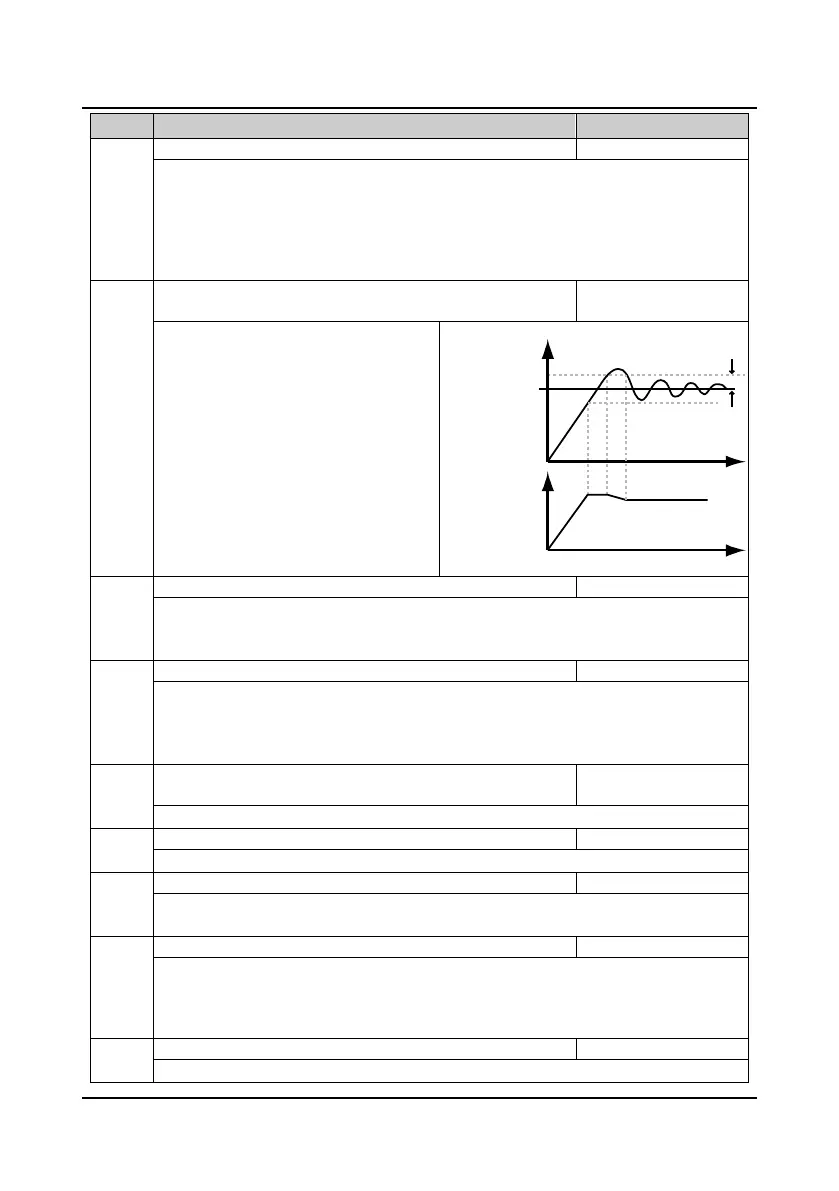

F04.10 Bias limit 0.0

20.0% (reference)

2.0%

F04.10 defines the maximum deviation of the

output from the reference closed-loop.

• PID regulator stops operation when the

feedback value is within this range.

• Setting this parameter correctly is

instructive to improve the system output

accuracy and stability.

F04.11 PID regulator upper limit source selection 0

2

0

0: Set by F04.13.

1: Set by AI analogue value. Set by analogue input voltage AI and refer to Group F16.

2: Set by terminal pulse input.

F04.12 PID regulator lower limit source selection 0

2

0

It defines the setting source of PID regulator lower limit value.

0: Set by F04.14.

1: Set by AI analogue value. Set by analogue input voltage AI and refer to Group F16.

2: Set by terminal pulse.

F04.13 PID regulator upper limit value 0.00

upper limit

50.00Hz

It defines that the process PID regulator output digital setting value of upper limit.

F04.14 PID regulator lower limit value 0.00

upper limit

0.00Hz

It defines that the process PID regulator output digital setting value of lower limit.

F04.15 PID regulator characteristic 0,1

0

0: Positive. The motor speed is required to increase with the increase of the reference.

1: Negative. The motor speed is required to decrease with the increase of the reference.

F04.16 Integral regulation selection 0,1

0

0: Stop integral regulation when the frequency reaches the upper or lower limit.

1: Continue the integral regulation when the frequency reaches the upper or lower limit.

• It is recommended to disable the integral regulation when the frequency reaches the upper or

lower limit on condition that fast response is needed.

F04.17 PID output filter time 0.01

10.00s

0.05

It defines the filtering time of process PID output.

Time

Output frequency

F04.10

Time

Feedback value

Reference value

Loading...

Loading...