Intel® Server Board S2600CO Family TPS Appendix F: POST Code Diagnostic LED Decoder

Revision 1.0

Intel order number G42278-002

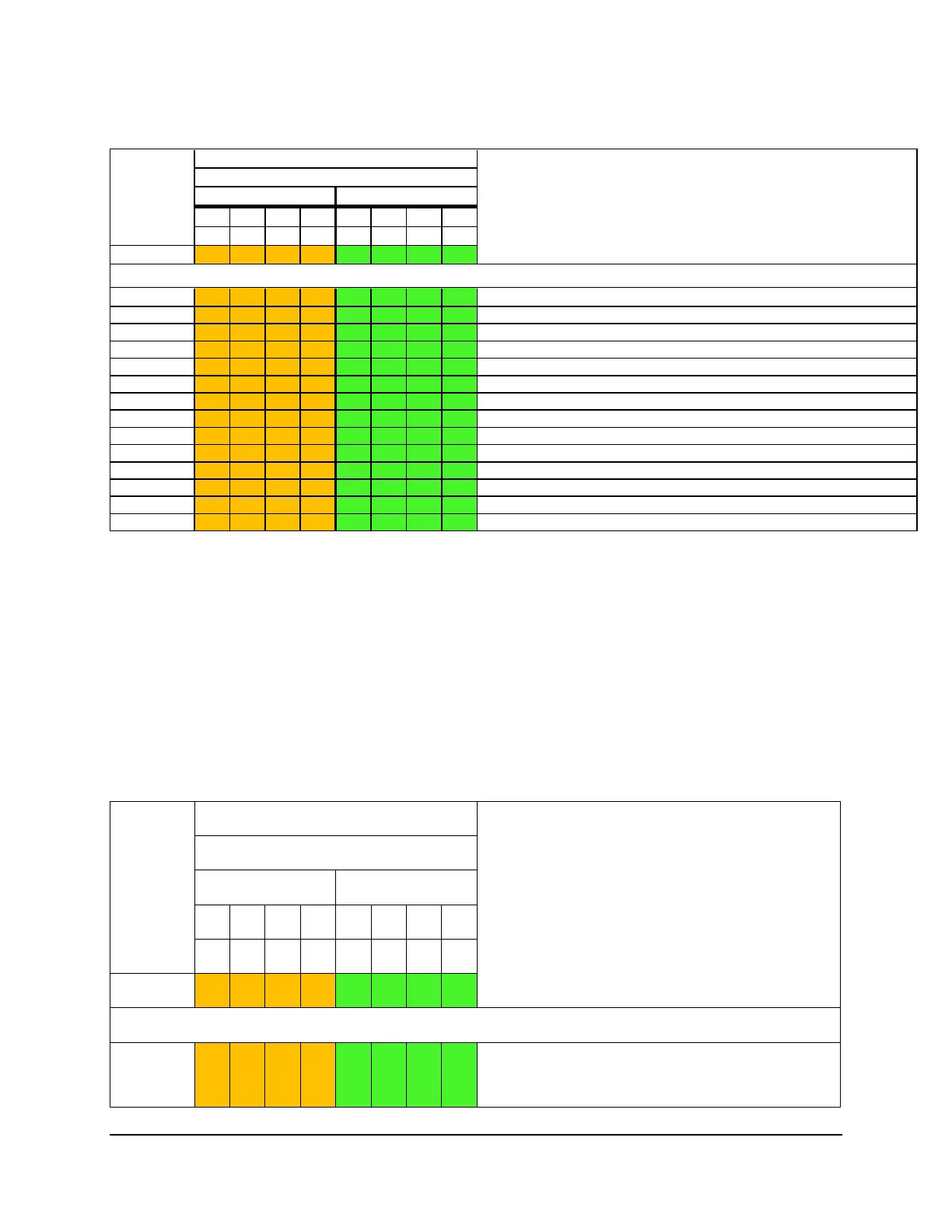

Table 78. MRC Progress Codes

Gather remaining SPD data

Program registers on the memory controller level

Evaluate RAS modes and save rank information

Program registers on the channel level

Perform the JEDEC defined initialization sequence

Hardware memory test and init

Execute software memory init

Program memory map and interleaving

Program RAS configuration

Memory Initialization at the beginning of POST includes multiple functions, including: discovery,

channel training, validation that DIMM population is acceptable and functional, initialization of

the IMC and other hardware settings, and initialization of applicable RAS configurations.

When a major memory initialization error occurs and prevents the system from booting with data

integrity, a beep code is generated, the MRC will display a fatal error code on the diagnostic

LEDs, and a system halt command is executed. Fatal MRC error halts do NOT change the state

of the System Status LED, and do NOT get logged as SEL events. The following table lists all

MRC fatal errors that are displayed to the Diagnostic LEDs.

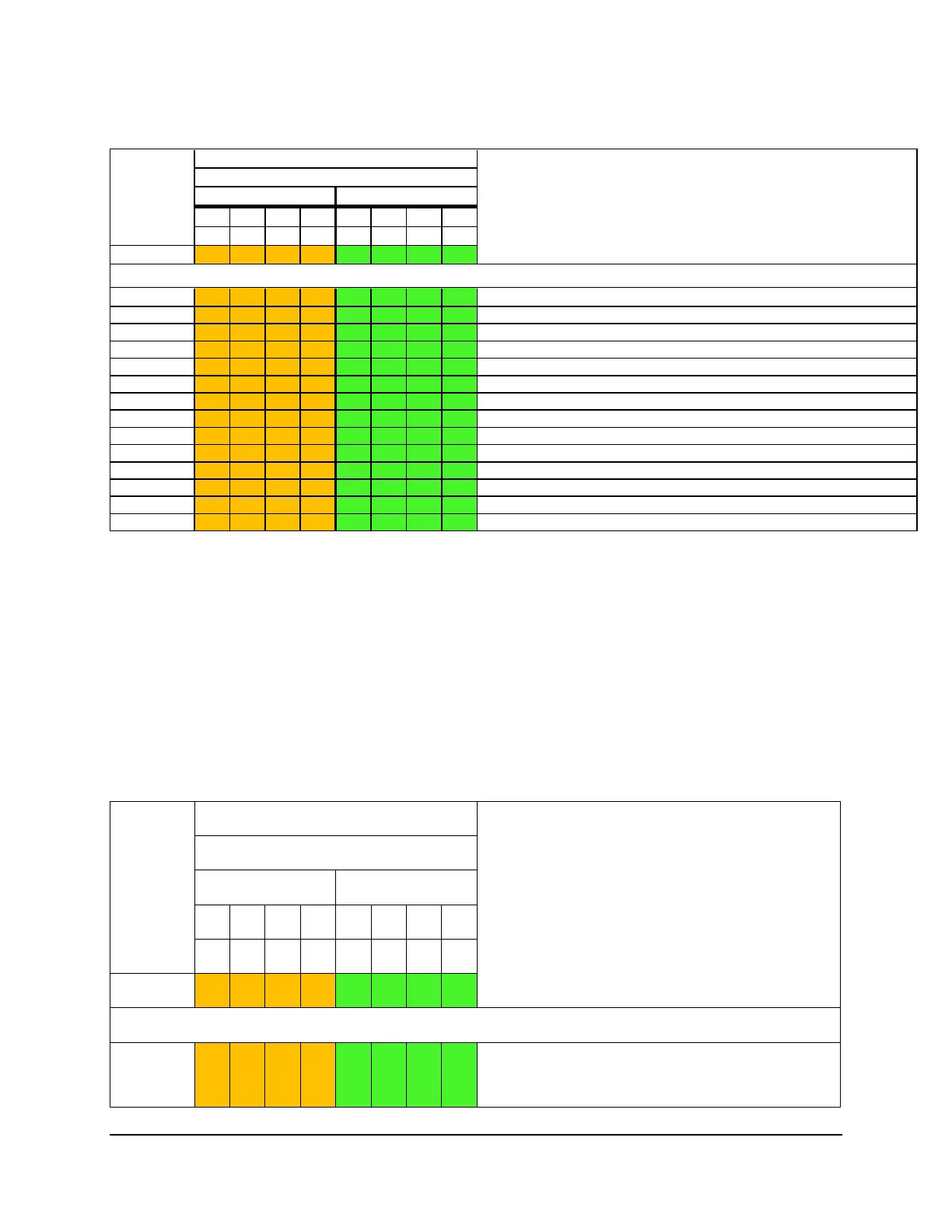

Table 79. MRC Fatal Error Codes

Description (with MRC Internal Minor Code)

No usable memory error

01h = No memory was detected from the SPD read, or

invalid config that causes no operable memory.

02h = Memory DIMMs on all channels of all sockets are

Loading...

Loading...