Intel® Xeon™ Processor with 800 MHz System Bus

Datasheet 19

NOTES:

1. Refer to Section 4.0 for signal descriptions.

2. The Intel® Xeon™ processor with 800 MHz system bus only uses BR0# and BR1#. BR2# and BR3# must be

terminated to V

TT

. For additional details regarding the BR[3:0]# signals, see Section 4.0 and Section 7.1.

3. The value of these pins during the active-to-inactive edge of RESET# defines the processor configuration

options. See Section 7.1 for details.

4. These signals may be driven simultaneously by multiple agents (wired-OR).

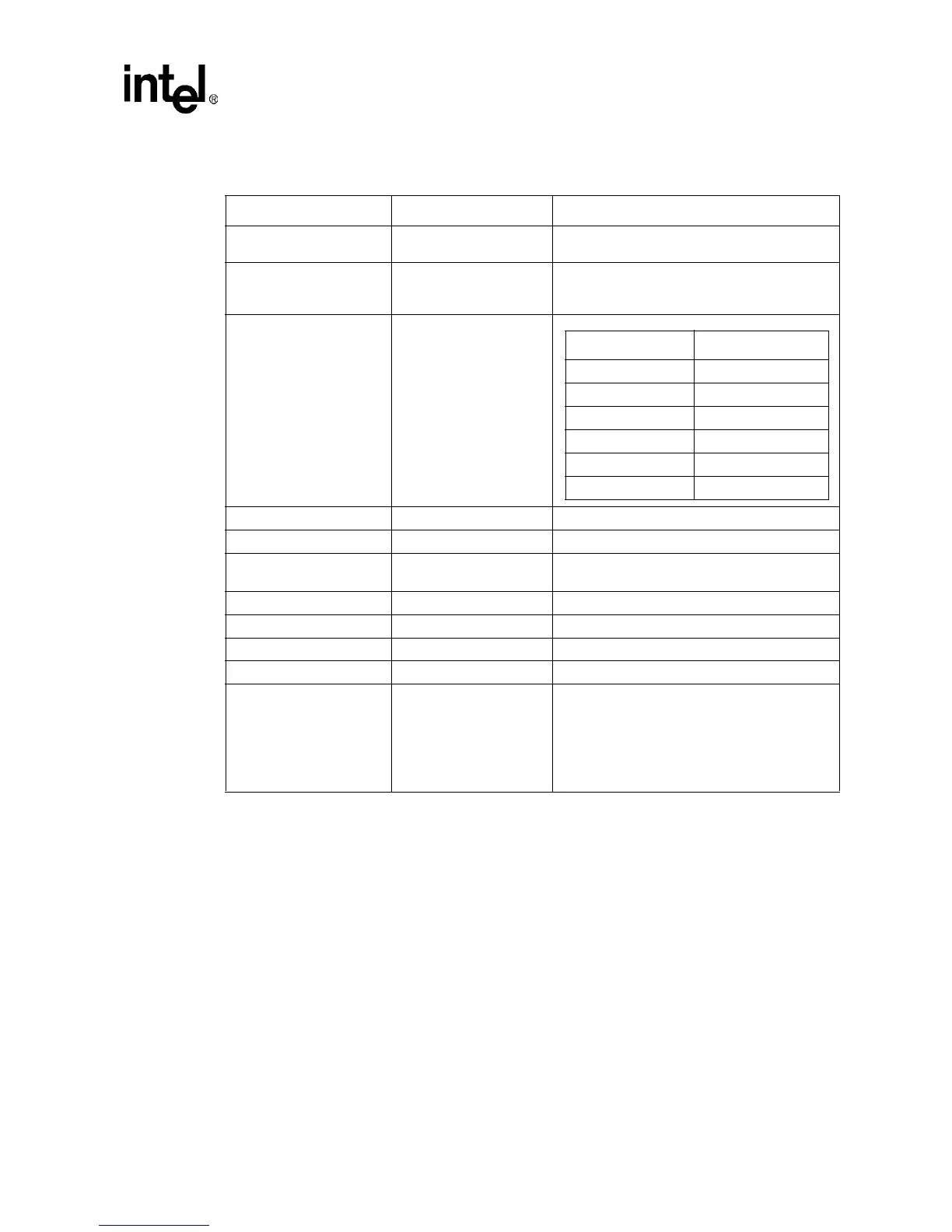

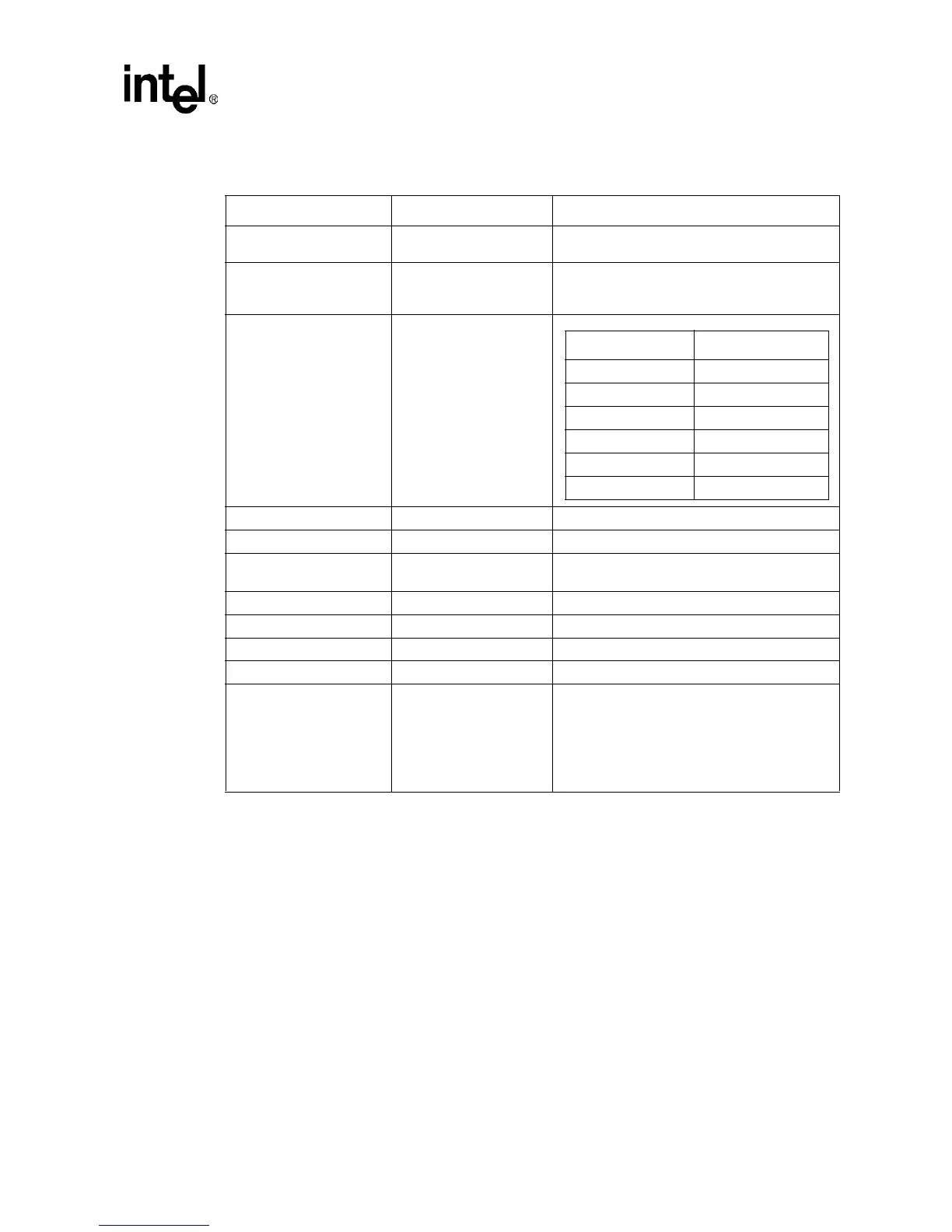

Table 5. Front Side Bus Signal Groups

Signal Group Type Signals

1

AGTL+ Common Clock

Input

Synchronous to BCLK[1:0] BPRI#, BR[3:1]#

2,3

, DEFER#, RESET#, RS[2:0]#,

RSP#, TRDY#

AGTL+ Common Clock I/O Synchronous to BCLK[1:0] ADS#, AP[1:0]#, BINIT#

4

, BNR#

4

, BPM[5:0]#,

BR0#

2,3

, DBSY#, DP[3:0]#, DRDY#, HIT#

4

,

HITM#

4

, LOCK#, MCERR#

4

AGTL+ Source

Synchronous I/O

Synchronous to assoc.

strobe

AGTL+ Strobe I/O Synchronous to BCLK[1:0] ADSTB[1:0]#, DSTBP[3:0]#, DSTBN[3:0]#

AGTL Asynchronous Output Asynchronous FERR#/PBE#, IERR#, PROCHOT#

GTL+ Asynchronous Input Asynchronous A20M#, FORCEPR#, IGNNE#, INIT#

3

, LINT0/

INTR, LINT1/NMI, SMI#

3

, SLP#, STPCLK#

GTL+ Asynchronous Output Asynchronous THERMTRIP#

Front Side Bus Clock Clock BCLK1, BCLK0

TAP Input Synchronous to TCK tck, tdi, tms, trst#

TAP Output Synchronous to TCK TDO

Power/Other Power/Other BOOT_SELECT, BSEL[1:0], COMP[1:0],

GTLREF[3:0], ODTEN, OPTIMIZED/COMPAT#,

PWRGOOD, Reserved, SKTOCC#,

SLEW_CTRL, SMB_PRT, TEST_BUS,

TESTHI[6:0], THERMDA, THERMDC, V

CC

, V

CCA

,

V

CCIOPLL,

V

CCPLL

, VCCSENSE, VID[5:0], V

SS

,

V

SSA

, VSSSENSE, V

TT

, VIDPWRGD, VTTEN

Signals Associated Strobe

REQ[4:0]#,A[16:3]#

3

ADSTB0#

A[35:17]#

3

ADSTB1#

D[15:0]#, DBI0# DSTBP0#, DSTBN0#

D[31:16]#, DBI1# DSTBP1#, DSTBN1#

D[47:32]#, DBI2# DSTBP2#, DSTBN2#

D[63:48]#, DBI3# DSTBP3#, DSTBN3#

Loading...

Loading...