Intel® Xeon™ Processor with 800 MHz System Bus

20 Datasheet

Table 6 outlines the signals which include on-die termination (R

TT

) and lists signals which include

additional on-die resistance (R

L

). O.pen drain signals are also included. Table 7 provides signal

reference voltages

NOTES:

1. Signals that do not have R

TT

, nor are actively driven to their high voltage level.

2. The termination for these signals is not R

TT

. The OPTIMIZED/COMPAT# and BOOT_SELECT pins have a

500 - 5000 Ω pull-up to V

TT

.

NOTES:

1. These signals also have hysteresis added to the reference voltage. See Table 14 for more information.

2.7 GTL+ Asynchronous and AGTL+ Asynchronous Signals

The Intel® Xeon™ processor with 800 MHz system bus does not use CMOS voltage levels on any

signals that connect to the processor silicon. As a result, input signals such as A20M#,

FORCEPR#, IGNNE#, INIT#, LINT0/INTR, LINT1/NMI, SMI#, SLP#, and STPCLK# use GTL

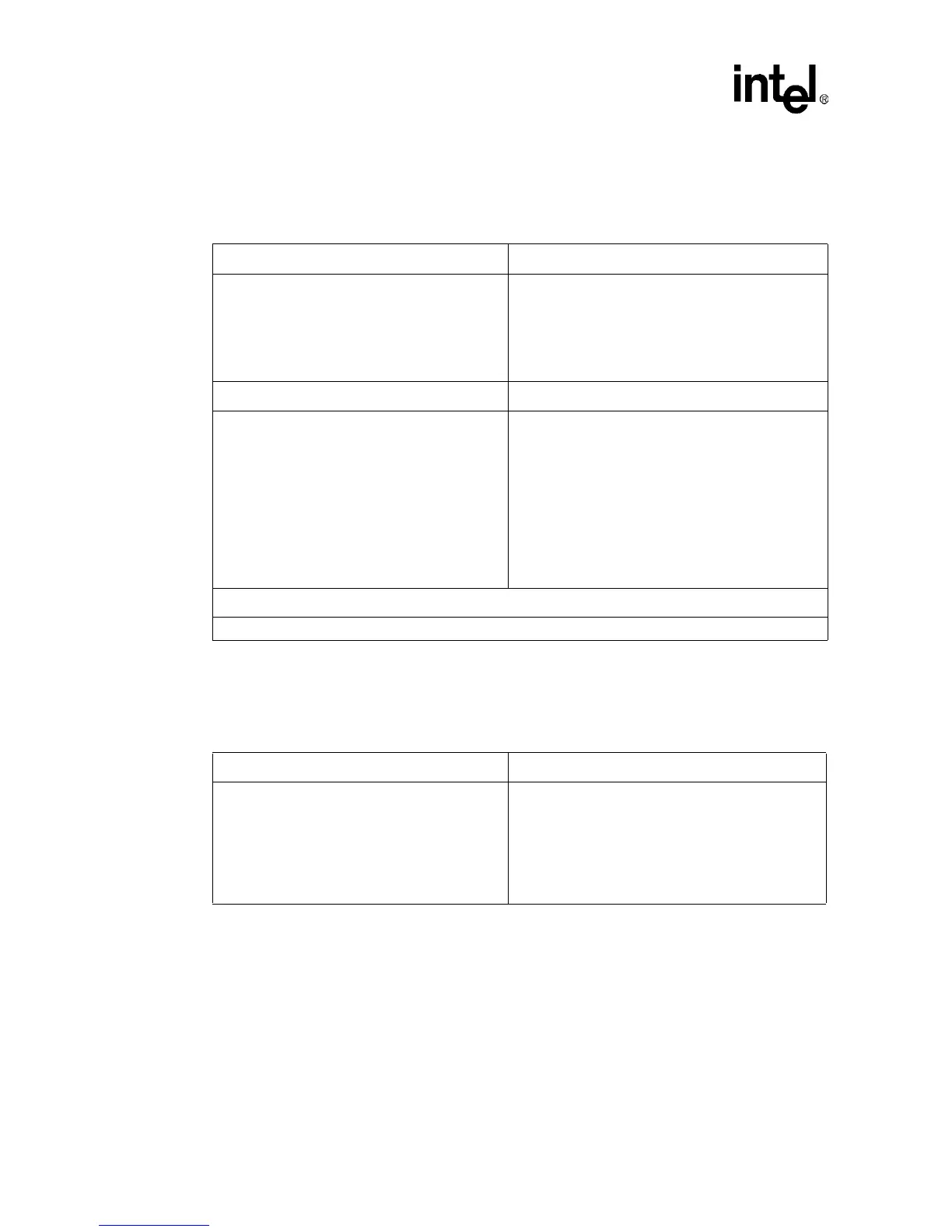

Table 6. Signal Description Table

Signals with R

TT

Signals with No R

TT

A[35:3]#, ADS#, ADSTB[1:0]#, AP[1:0]#, BINIT#,

BNR#, BOOT_SELECT

2

, BPRI#, D[63:0]#,

DBI[3:0]#, DBSY#, DEFER#, DP[3:0]#, DRDY#,

DSTBN[3:0]#, DSTBP[3:0]#, FORCEPR#, HIT#,

HITM#, LOCK#, MCERR#, OPTIMIZED/

COMPAT#

2

, REQ[4:0]#, RS[2:0]#, RSP#,

SLEW_CTRL, TEST_BUS, TRDY#

A20M#, BCLK[1:0], BPM[5:0]#, BR[3:0]#, BSEL[1:0],

COMP[1:0], FERR#/PBE#, GTLREF[3:0], IERR#,

IGNNE#, INIT#, LINT0/INTR, LINT1/NMI, ODTEN,

PROCHOT#, PWRGOOD, RESET#, SKTOCC#, SLP#,

SMI#, STPCLK#, TCK, TDI, TDO, TESTHI[6:0],

THERMDA, THERMDC, THERMTRIP#, TMS, TRST#,

VID[5:0], VIDPWRGD, VTTEN

Signals with R

L

Signals with No R

L

BINIT#, BNR#, HIT#, HITM#, MCERR# A20M#, A[35:3]#, ADS#, ADSTB[1:0]#, AP[1:0]#,

BCLK[1:0], BPM[5:0]#, BPRI#, BR[3:0]#, BSEL[1:0],

BOOT_SELECT

2

, COMP[1:0], D[63:0]#, DBI[3:0]#,

DBSY#, DEFER#, DP[3:0]#, DRDY#, DSTBN[3:0]#,

DSTBP[3:0]#, FERR#/PBE#, FORCEPR#,

GTLREF[3:0], IERR#, IGNNE#, INIT#, LINT0/INTR,

LINT1/NMI, LOCK#, ODTEN, OPTIMIZED/COMPAT#

2

,

PROCHOT#, PWRGOOD, REQ[4:0]#, RESET#,

RS[2:0]#, RSP#, SKTOCC#, SLEW_CTRL, SLP#, SMI#,

STPCLK#, TCK, TDI, TDO, TEST_BUS, TESTHI[6:0],

THERMDA, THERMDC, THERMTRIP#, TMS, TRDY#,

TRST#, VID[5:0], VIDPWRGD, VTTEN

Open Drain Signals

1

BPM[5:0]#, BR0#, BSEL[1:0], FERR#/PBE#, IERR#, TDO, THERMTRIP#, VID[5:0]

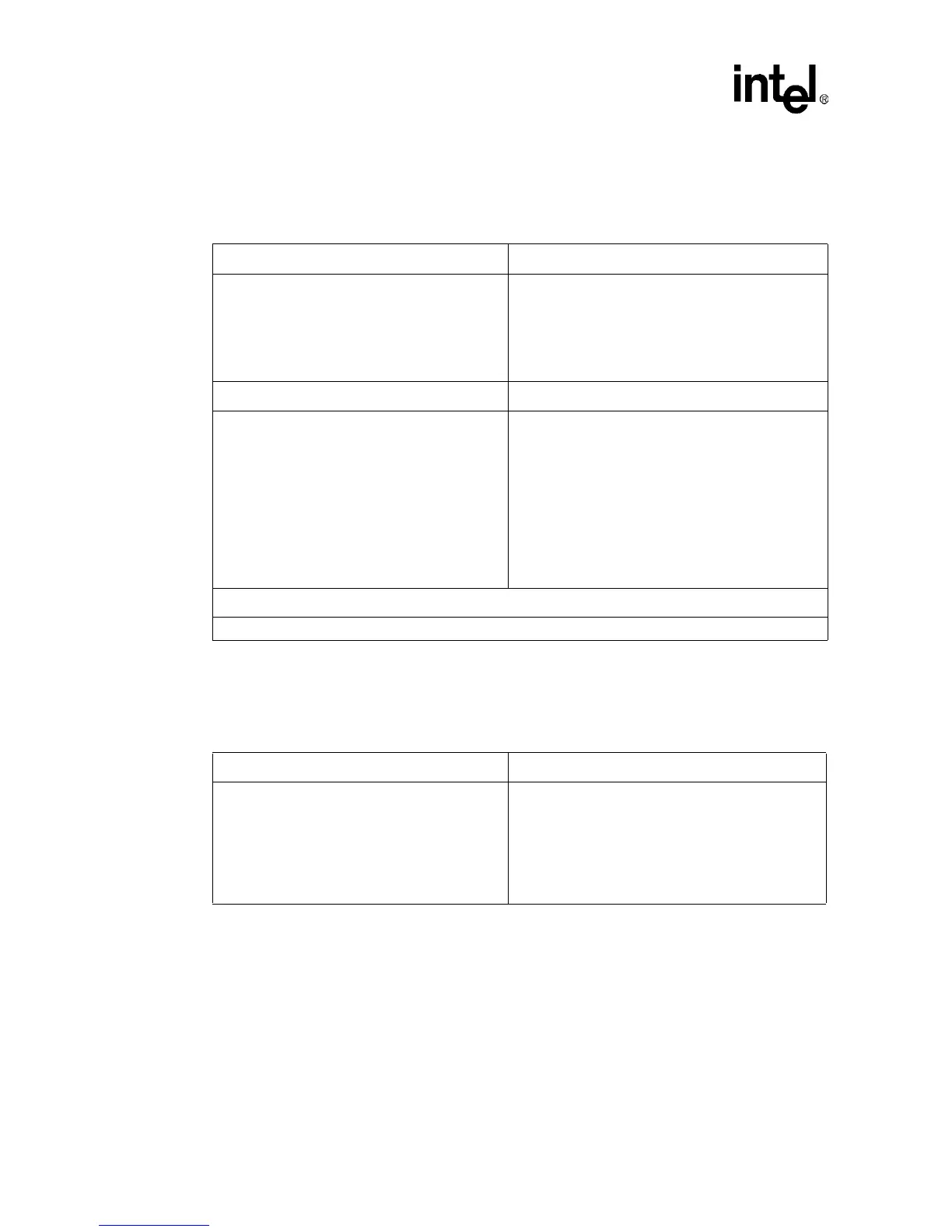

Table 7. Signal Reference Voltages

GTLREF 0.5 * V

TT

A20M#, A[35:3]#, ADS#, ADSTB[1:0]#, AP[1:0]#,

BINIT#, BNR#, BPM[5:0]#, BPRI#, BR[3:0]#,

D[63:0]#, DBI[3:0]#, DBSY#, DEFER#, DP[3:0]#,

DRDY#, DSTBN[3:0]#, DSTBP[3:0]#, FORCEPR#,

HIT#, HITM#, IGNNE#, INIT#, LINT0/INTR, LINT1/

NMI, LOCK#, MCERR#, ODTEN, RESET#,

REQ[4:0]#, RS[2:0]#, RSP#, SLEW_CTRL, SLP#,

SMI#, STPCLK#, TRDY#

BOOT_SELECT, OPTIMIZED/COMPAT#, PWRGOOD

1

,

TCK

1

, TDI

1

, TMS

1

, TRST#

1

, VIDPWRGD

Loading...

Loading...