Chapter 13 Installation and Wiring

13 5

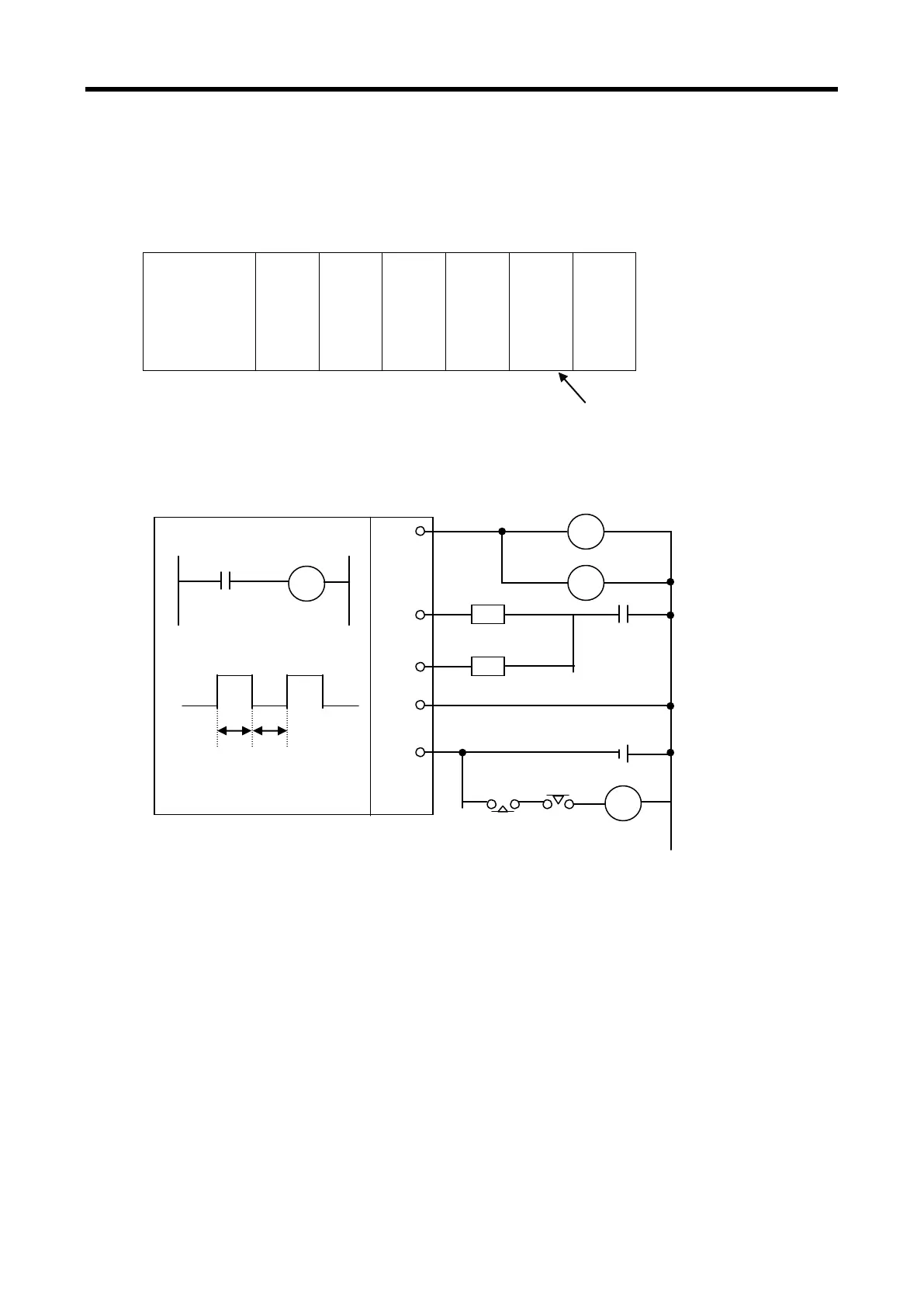

(3) Fail safe countermeasure in case of PLC error

Error of PLC CPU and memory is detected by self diagnosis but in case error occurs in IO control part, etc.,

CPU can detect the error. At this case, though it is different according to status of error, all contact point is on

or off, so safety may not be guaranteed. Though we do out best to our quality as producer, configure safety

circuit preparing that error occurs in PLC and it lead to breakdown or accident.

System example

Equip output module for fail safe to last slot of system.

[Fail safe circuit example]

Since P80 turn on/off every 0.5s, use TR output.

Output module for fail safe

Loading...

Loading...