2. INSTRUCTIONS

2 − 19

MELSEC-A

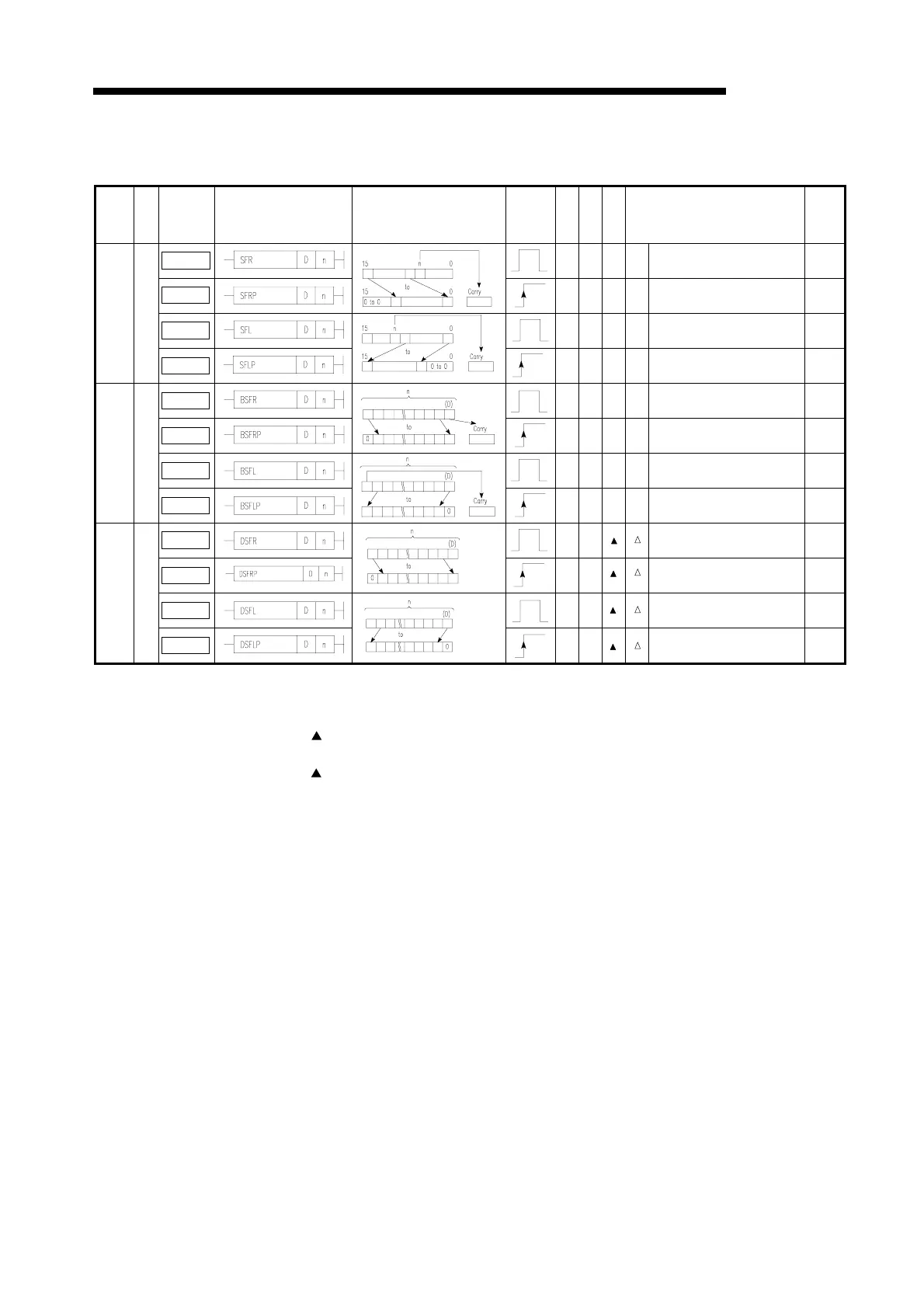

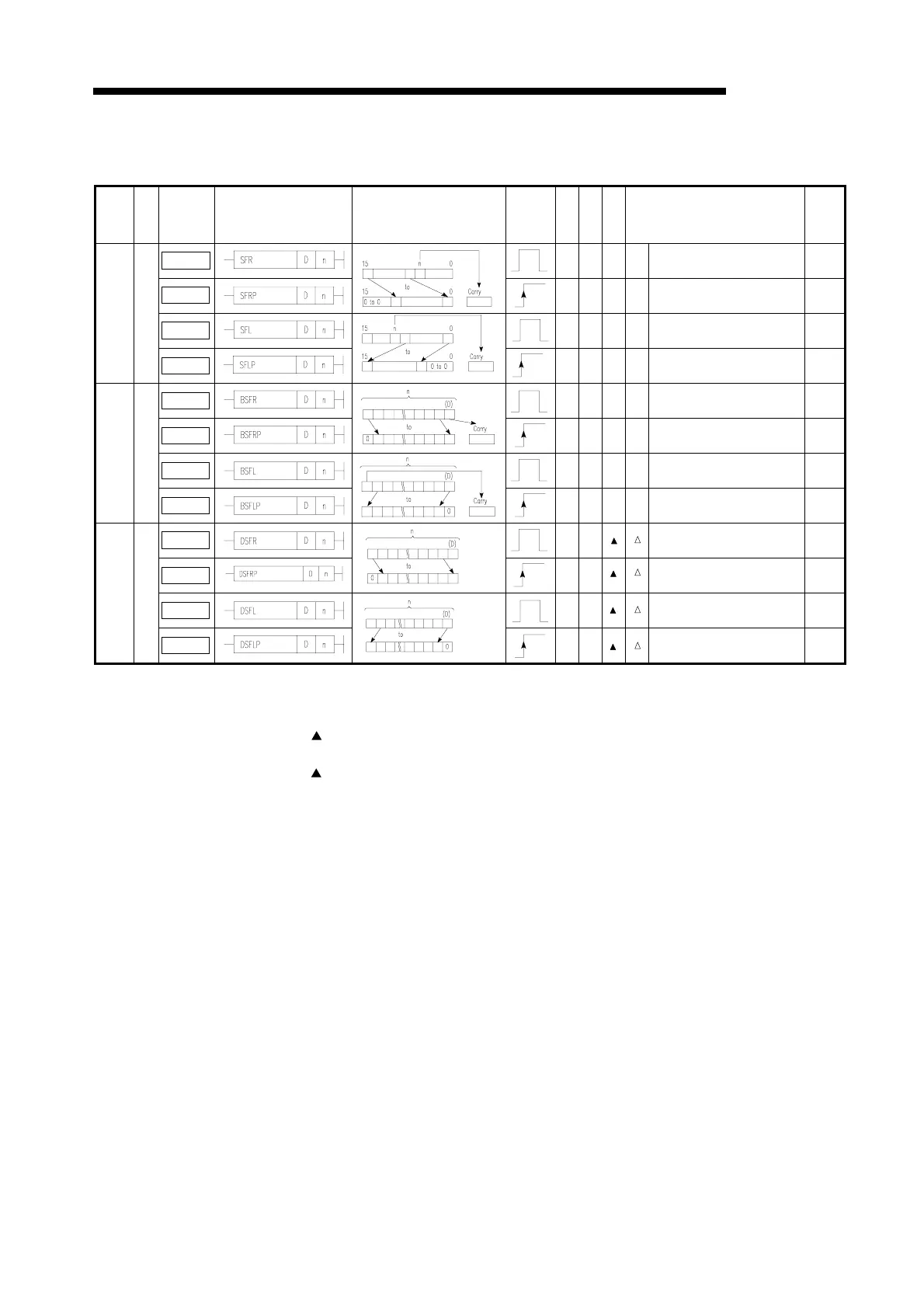

(3) Shift instructions

Table 2.19 Shift Instructions

Classi-

fication

Unit

Instruction

Symbol

Symbol Contents of Processing

Execu-

tion Con-

dition

Number

of steps

Index

Subset

Applicable CPU Page

SFR

5

● ●

!

7-32

SFRP

5

● ●

!

7-32

SFL

5

● ●

!

7-32

n bit

shift

16 bits

SFLP

5

● ●

!

7-32

BSFR

7

●

!

7-35

BSFRP

7

●

!

7-35

BSFL

7

●

!

7-35

1 bit

shift

n bit

BSFLP

7

●

!

7-35

DSFR

7

●

Not applicable to A73 7-37

DSFRP

7

●

Not applicable to A73 7-37

DSFL

7

●

Not applicable to A73 7-37

1 ward

shift

n ward

DSFLP

7

●

Not applicable to A73 7-37

*1: For the number of steps when extension devices are used or when index qualification is performed to

bit devices for AnA, A2AS, AnU, QCPU-A (A Mode) and A2USH board, refer to Section 3.8.1.

*2: The

mark in the Index column indicates that index qualification can be performed with the AnA,

A2AS, AnU, QCPU-A (A Mode) and A2USH board only.

*3: The

mark in the Subset column indicates that subset processing can be performed with the A3H,

A3M, AnA, A2AS, AnU, QCPU-A (A Mode) and A2USH board only.

*1

*3

*3

*3

*3

Loading...

Loading...