APPENDICES

APP − 76

MELSEC-A

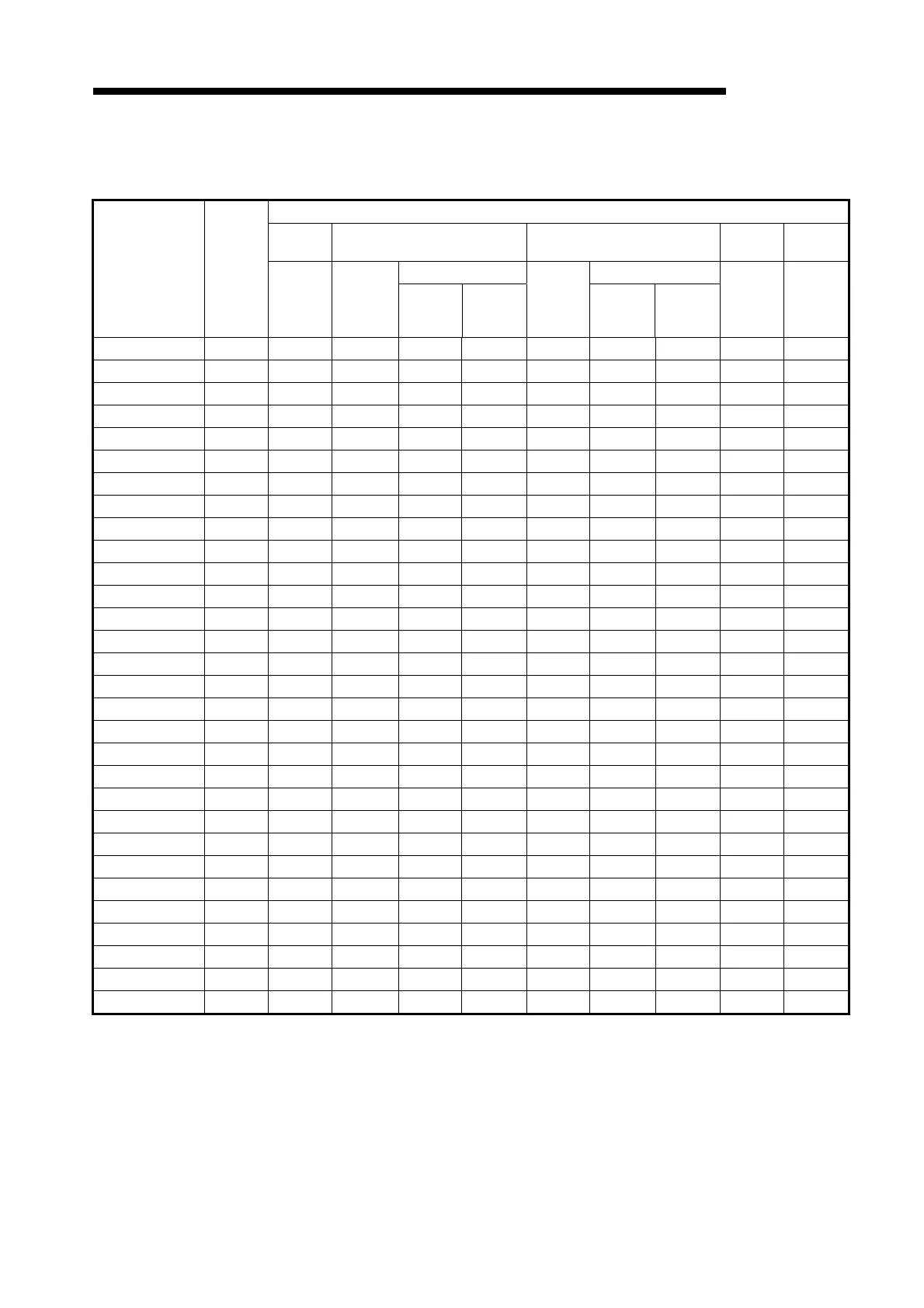

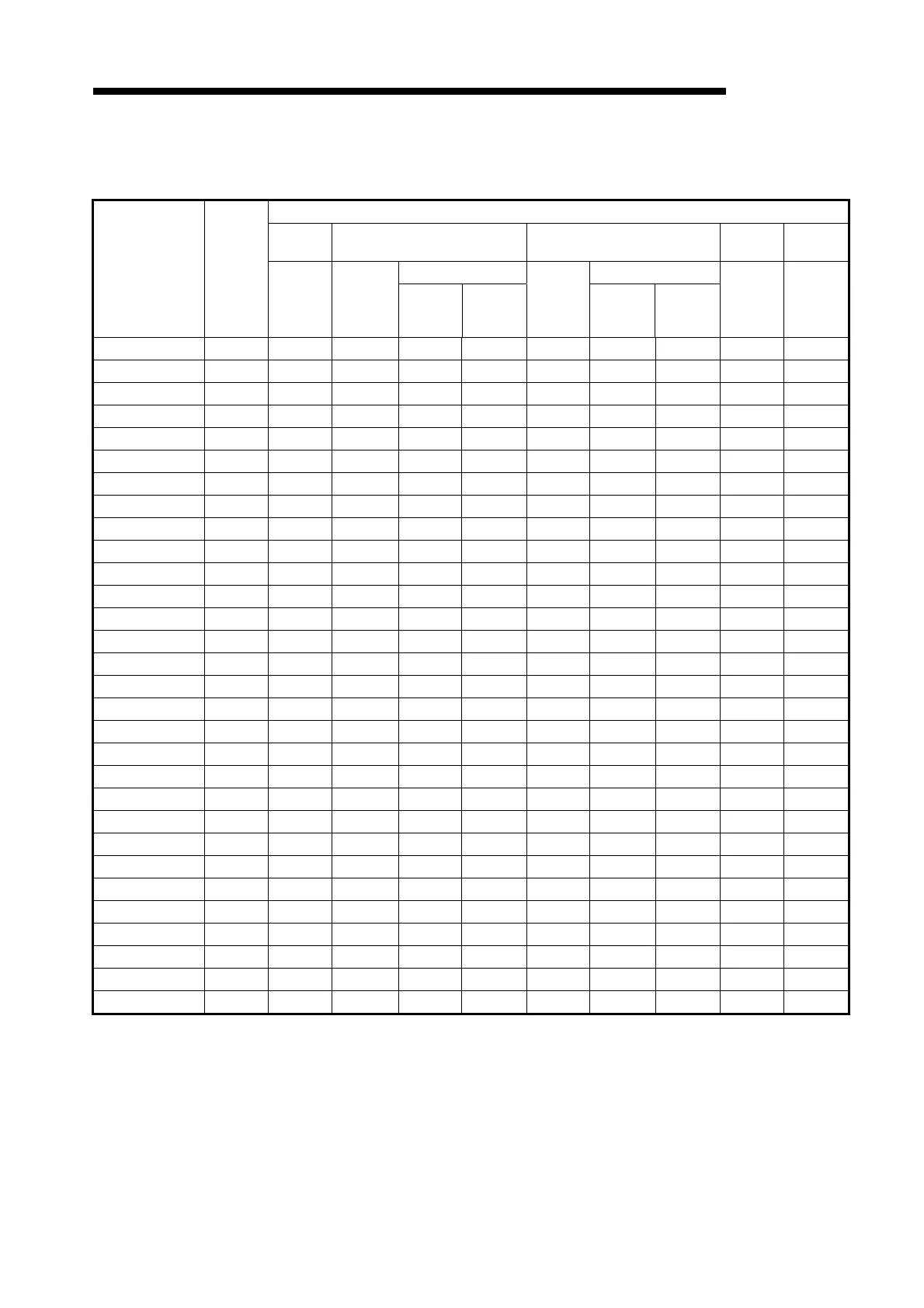

(3) Application instructions

Table 2.6 Instruction Processing Time of CPUs

Processing Time (µs)

An

AnN, A3V, A73

A3N Board

A3H, A3M A2A, A2U

A3A

A3U, A4U

D D

Instruction Condition

D R

Other

than

X, Y

X, Y

R

Other

than

X, Y

X, Y

R R

WAND S D 90 60 59 72 1.6 1.6 9.2 2.8 2.1

WANDP S D 90 60 59 72 1.6 1.6 9.2 2.8 2.1

DAND 276 140 139 240 27 27 43 13 9.5

DANDP 276 140 139 240 27 27 43 13 9.5

WAND S1 S2 D 179 96 96 152 21 21 32 7.6 5.7

WANDP S1 S2 D

179 96 96 152 21 21 32 7.6 5.7

WOR S D 90 61 60 72 1.6 1.6 9.2 2.8 2.1

WORP S D 90 61 60 72 1.6 1.6 9.2 2.8 2.1

DOR 276 140 139 240 27 27 43 13 9.5

DORP 276 140 139 240 27 27 43 13 9.5

WOR S1 S2 D 176 97 96 152 21 21 32 7.6 5.7

WORP S1 S2 D 176 97 96 152 21 21 32 7.6 5.7

WXOR S D 91 60 59 72 1.6 1.6 9.2 2.8 2.1

WXORP S D 91 60 59 72 1.6 1.6 9.2 2.8 2.1

DXOR 274 140 139 240 27 27 43 13 9.5

DXORP 274 140 139 240 27 27 43 13 9.5

WXOR S1 S2 D 178 97 96 152 21 21 32 7.6 5.7

WXORP S1 S2 D

178 97 96 152 21 21 32 7.6 5.7

WXNR S D 89 64 62 74 1.6 1.6 9.2 3.0 2.3

WXNRP S D 89 64 62 74 1.6 1.6 9.2 3.0 2.3

DXNR 277 142 140 241 27 27 43 15 11

DXNRP 277 142 140 241 27 27 43 15 11

WXNR S1 S2 D 177 98 96 152 21 21 32 7.8 5.9

WXNRP S1 S2 D

177 98 96 152 21 21 32 7.8 5.9

NEG 105 50 49 86 14 14 18 8.6 6.5

NEGP 105 50 49 86 14 14 18 8.6 6.5

ROR n n=5 66 52 51 51 4.8 4.8 4.8 5.8 4.4

RORP n n=5 66 52 51 51 4.8 4.8 4.8 5.8 4.4

RCR n n=5 74 59 59 59 6.8 6.8 6.8 6.4 4.8

RCRP n n=5 74 59 59 59 6.8 6.8 6.8 6.4 4.8

R: Refresh mode, D: Direct mode

Loading...

Loading...