8- 4 MC68000 8-/16-/32-MICROPROCESSORS UISER'S MANUAL MOTOROLA

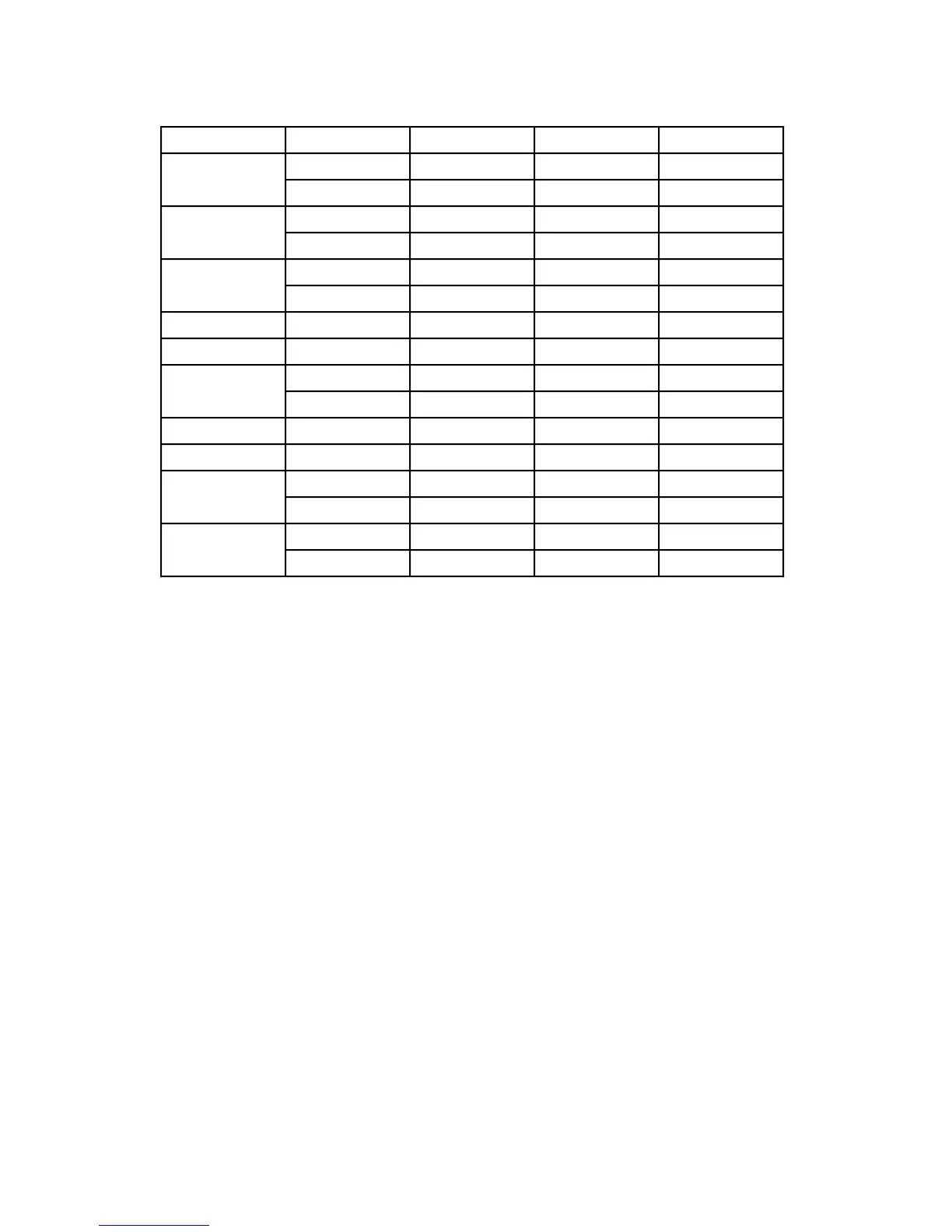

Table 8-4. Standard Instruction Execution Times

Instruction Size op<ea>, An† op<ea>, Dn op Dn, <M>

ADD/ADDA Byte, Word 8(1/0)+ 4(1/0)+ 8(1/1)+

Long 6(1/0)+** 6(1/0)+** 12(1/2)+

AND Byte, Word — 4(1/0)+ 8(1/1)+

Long — 6(1/0)+** 12(1/2)+

CMP/CMPA Byte, Word 6(1/0)+ 4(1/0)+ —

Long 6(1/0)+ 6(1/0)+ —

DIVS — — 158(1/0)+* —

DIVU — — 140(1/0)+* —

EOR Byte, Word — 4(1/0)*** 8(1/1)+

Long — 8(1/0)*** 12(1/2)+

MULS — — 70(1/0)+* —

MULU — — 70(1/0)+* —

OR Byte, Word — 4(1/0)+ 8(1/1)+

Long — 6(1/0)+** 12(1/2)+

SUB Byte, Word 8(1/0)+ 4(1/0)+ 8(1/1)+

Long 6(1/0)+** 6(1/0)+** 12(1/2)+

+ Add effective address calculation time.

† Word or long only

* Indicates maximum basic value added to word effective address time

** The base time of six clock periods is increased to eight if the effective address mode is

register direct or immediate (effective address time should also be added).

*** Only available effective address mode is data register direct.

DIVS, DIVU — The divide algorithm used by the MC68000 provides less than 10% difference

between the best- and worst-case timings.

MULS, MULU — The multiply algorithm requires 38+2n clocks where n is defined as:

MULU: n = the number of ones in the <ea>

MULS: n=concatenate the <ea> with a zero as the LSB; n is the resultant number of 10

or 01 patterns in the 17-bit source; i.e., worst case happens when the source

is $5555.

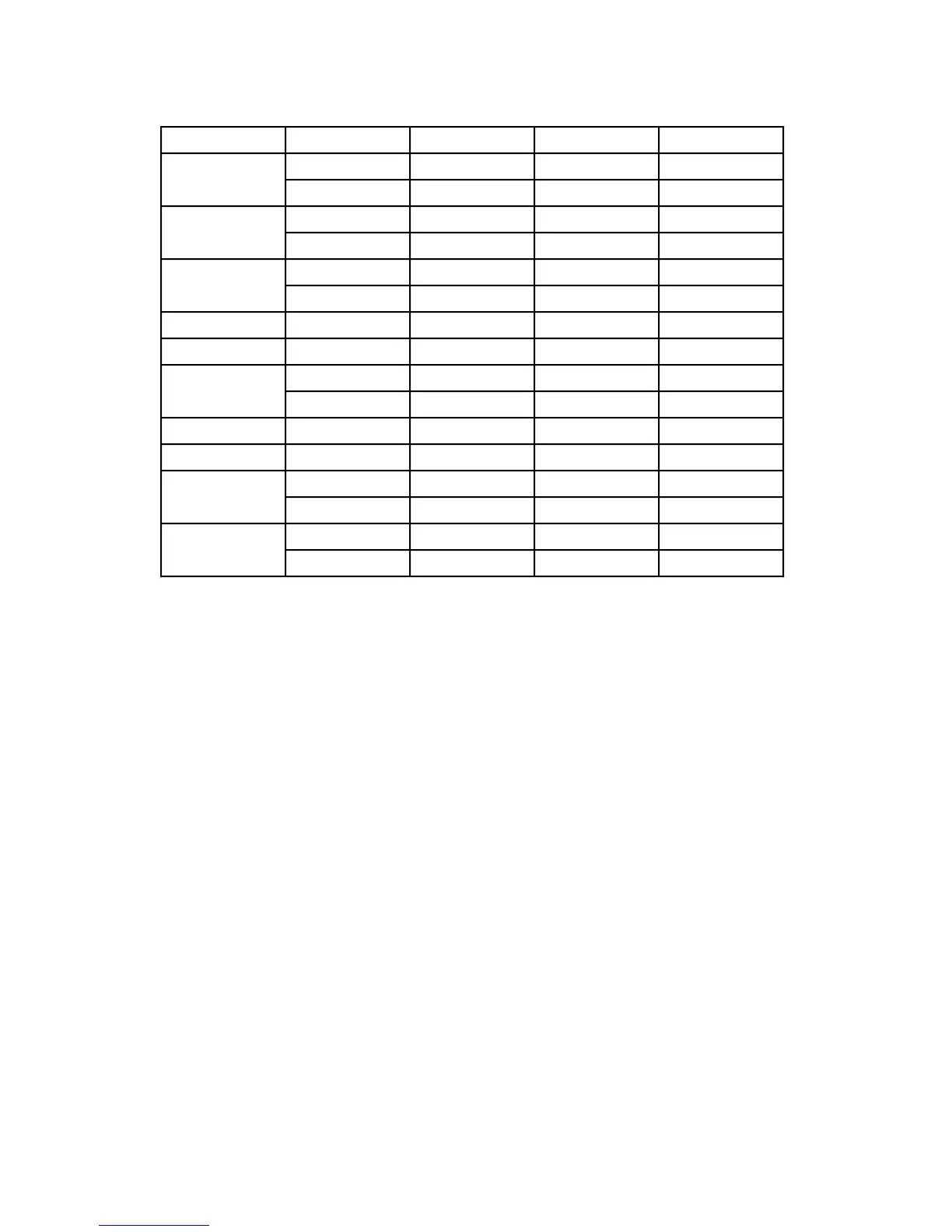

8.4 IMMEDIATE INSTRUCTION EXECUTION TIMES

The numbers of clock periods shown in Table 8-5 include the times to fetch immediate

operands, perform the operations, store the results, and read the next operation. The total

number of clock periods, the number of read cycles, and the number of write cycles are

shown in the previously described format. The number of clock periods, the number of

read cycles, and the number of write cycles, respectively, must be added to those of the

effective address calculation where indicated by a plus sign (+).

In Table 8-5, the following notation applies:

# — Immediate operand

Dn — Data register operand

An — Address register operand

M — Memory operand

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...