MOTOROLA M68000 8-/16-/32-BIT MICROPROCESSORS USER’S MANUAL 9- 9

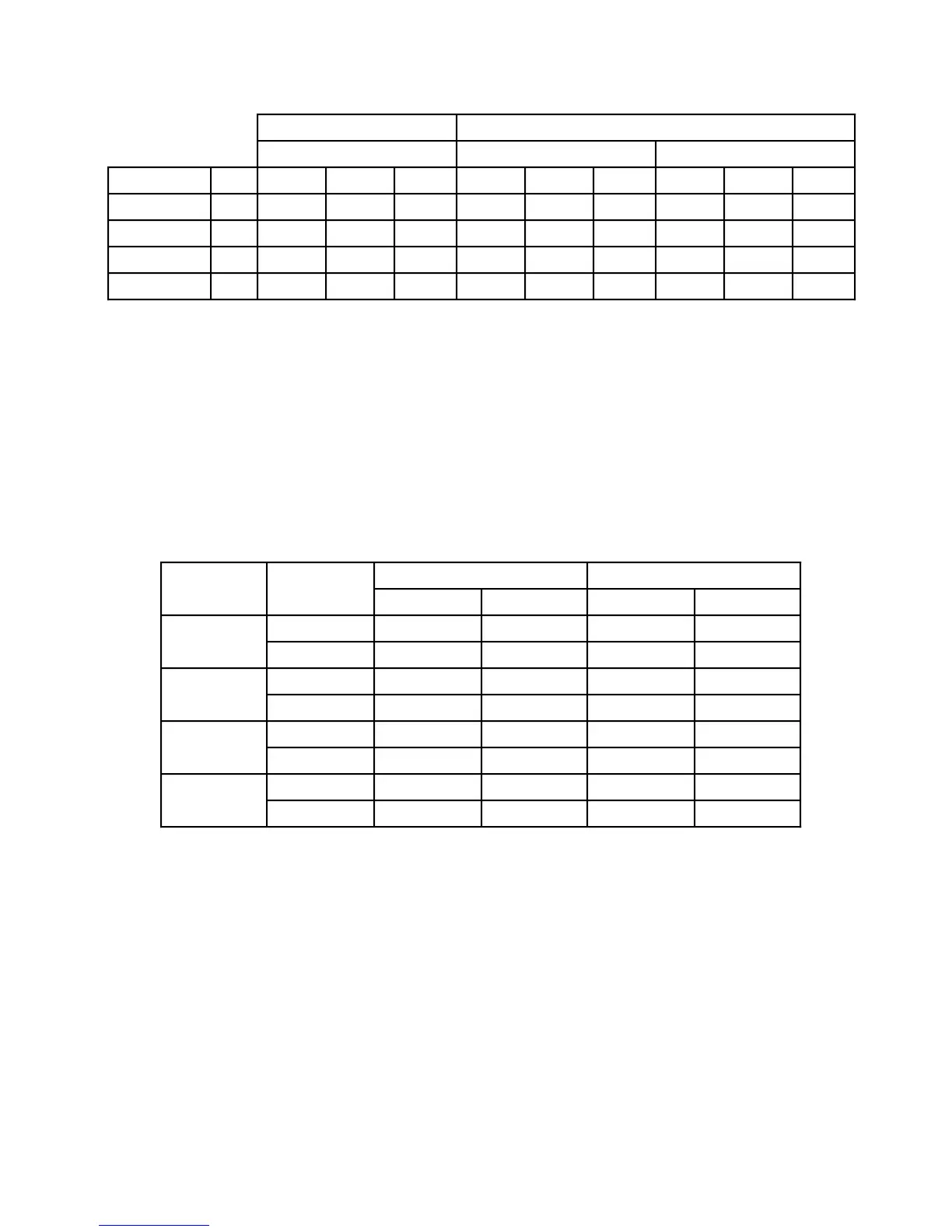

Table 9-13. Shift/Rotate Instruction Loop Mode Execution Times

Loop Continued Loop Terminated

Valid Count cc False Valid Count cc True Expired Count

Instruction Size (An) (An)+ –(An) (An) (An)+ –(An) (An) (An)+ –(An)

ASR, ASL Word 18(1/1) 18(1/1) 20(1/1) 24(3/1) 24(3/1) 26(3/1) 22(3/1) 22(3/1) 24(3/1)

LSR, LSL Word 18(1/1) 18(1/1) 20(1/1) 24(3/1) 24(3/1) 26(3/1) 22(3/1) 22(3/1) 24(3/1)

ROR, ROL Word 18(1/1) 18(1/1) 20(1/1) 24(3/1) 24(3/1) 26(3/1) 22(3/1) 22(3/1) 24(3/1)

ROXR, ROXL Word 18(1/1) 18(1/1) 20(1/1) 24(3/1) 24(3/1) 26(3/1) 22(3/1) 22(3/1) 24(3/1)

9.7 BIT MANIPULATION INSTRUCTION EXECUTION TIMES

Table 9-14 lists the timing data for the bit manipulation instructions. The total number of

clock periods, the number of read cycles, and the number of write cycles are shown in the

previously described format. The number of clock periods, the number of read cycles, and

the number of write cycles, respectively, must be added to those of the effective address

calculation where indicated by a plus sign (+).

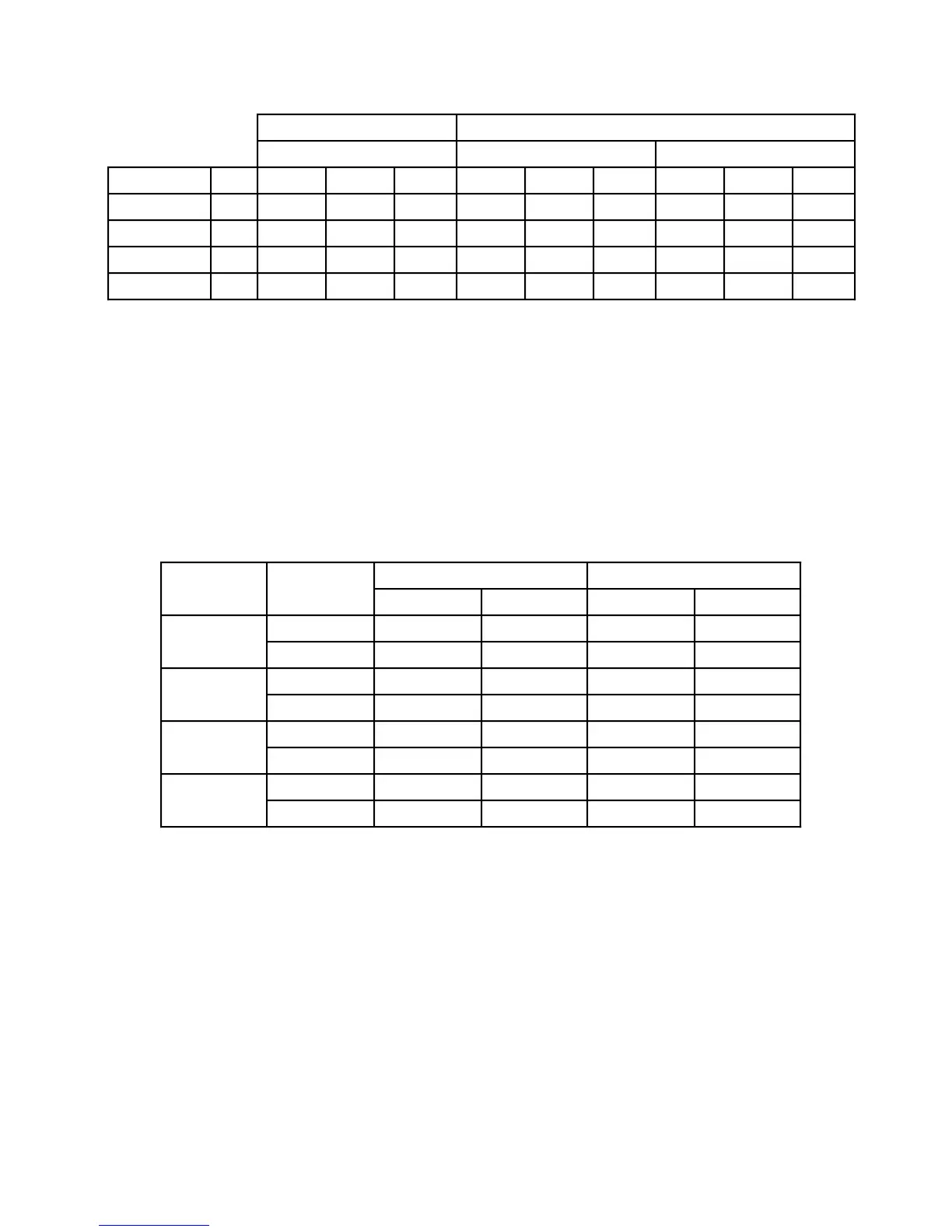

Table 9-14. Bit Manipulation Instruction Execution Times

Dynamic Static

Instruction Size Register Memory Register Memory

BCHG Byte — 8(1/1)+ — 12(2/1)+

Long 8(1/0)* — 12(2/0)* —

BCLR Byte — 10(1/1)+ — 14(2/1)+

Long 10(1/0)* — 14(2/0)* —

BSET Byte — 8(1/1)+ — 12(2/1)+

Long 8(1/0)* — 12(2/0)* —

BTST Byte — 4(1/0)+ — 8(2/0)+

Long 6(1/0)* — 10(2/0) —

+Add effective address calculation time.

* Indicates maximum value; data addressing mode only.

9.8 CONDITIONAL INSTRUCTION EXECUTION TIMES

Table 9-15 lists the timing data for the conditional instructions. The total number of clock

periods, the number of read cycles, and the number of write cycles are shown in the

previously described format.

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...