8- 6 MC68000 8-/16-/32-MICROPROCESSORS UISER'S MANUAL MOTOROLA

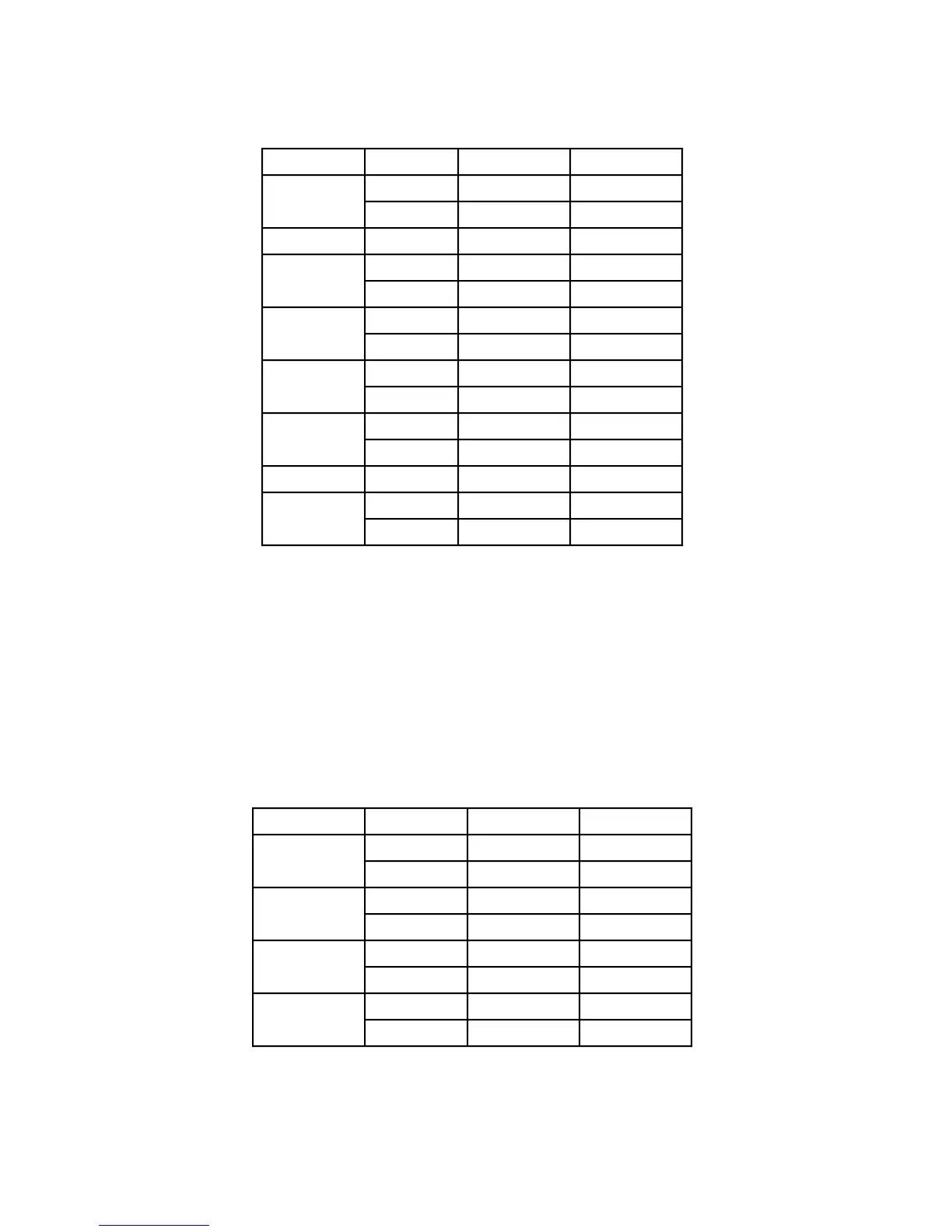

Table 8-6. Single Operand Instruction

Execution Times

Instruction Size Register Memory

CLR Byte, Word 4(1/0) 8(1/1)+

Long 6(1/0) 12(1/2)+

NBCD Byte 6(1/0) 8(1/1)+

NEG Byte, Word 4(1/0) 8(1/1)+

Long 6(1/0) 12(1/2)+

NEGX Byte, Word 4(1/0) 8(1/1)+

Long 6(1/0) 12(1/2)+

NOT Byte, Word 4(1/0) 8(1/1)+

Long 6(1/0) 12(1/2)+

Scc Byte, False 4(1/0) 8(1/1)+

Byte, True 6(1/0) 8(1/1)+

TAS Byte 4(1/0) 14(2/1)+

TST Byte, Word 4(1/0) 4(1/0)+

Long 4(1/0) 4(1/0)+

+Add effective address calculation time.

8.6 SHIFT/ROTATE INSTRUCTION EXECUTION TIMES

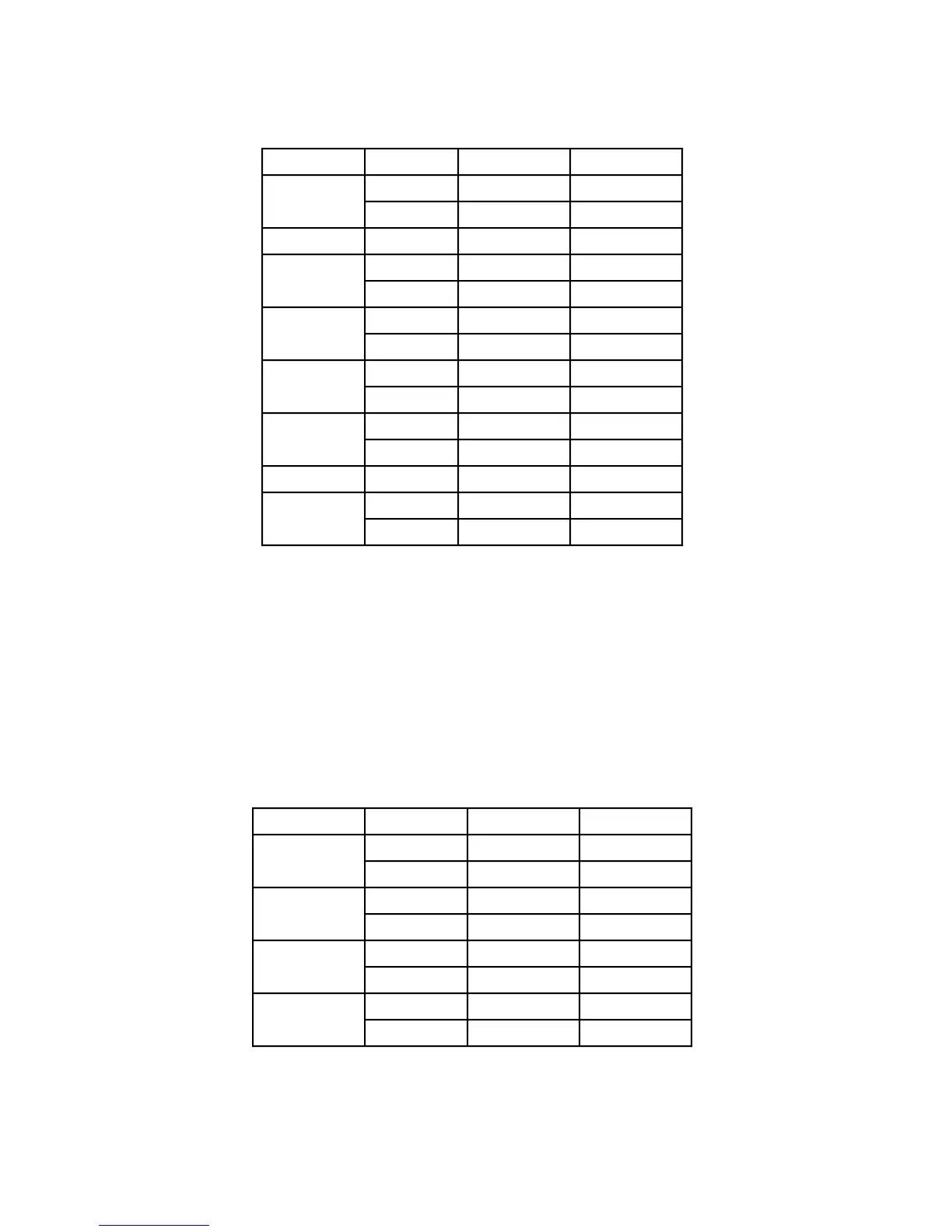

Table 8-7 lists the timing data for the shift and rotate instructions. The total number of

clock periods, the number of read cycles, and the number of write cycles are shown in the

previously described format. The number of clock periods, the number of read cycles, and

the number of write cycles, respectively, must be added to those of the effective address

calculation where indicated by a plus sign (+).

Table 8-7. Shift/Rotate Instruction Execution Times

Instruction Size Register Memory

ASR, ASL Byte, Word 6+2n(1/0) 8(1/1)+

Long 8+2n(1/0) —

LSR, LSL Byte, Word 6+2n(1/0) 8(1/1)+

Long 8+2n(1/0) —

ROR, ROL Byte, Word 6+2n(1/0) 8(1/1)+

Long 8+2n(1/0) —

ROXR, ROXL Byte, Word 6+2n(1/0) 8(1/1)+

Long 8+2n(1/0) —

+Add effective address calculation time for word operands.

n is the shift count.

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...