MOTOROLA M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL 10-17

10.12 AC ELECTRICAL SPECIFICATIONS — BUS ARBITRATION (V

CC

=5.0

VDC±5%; GND=0 VDC, T

A

=T

L

TO T

H

; See Figure s 10-7 – 10-11) (Applies To All Processors

Except The MC68EC000)

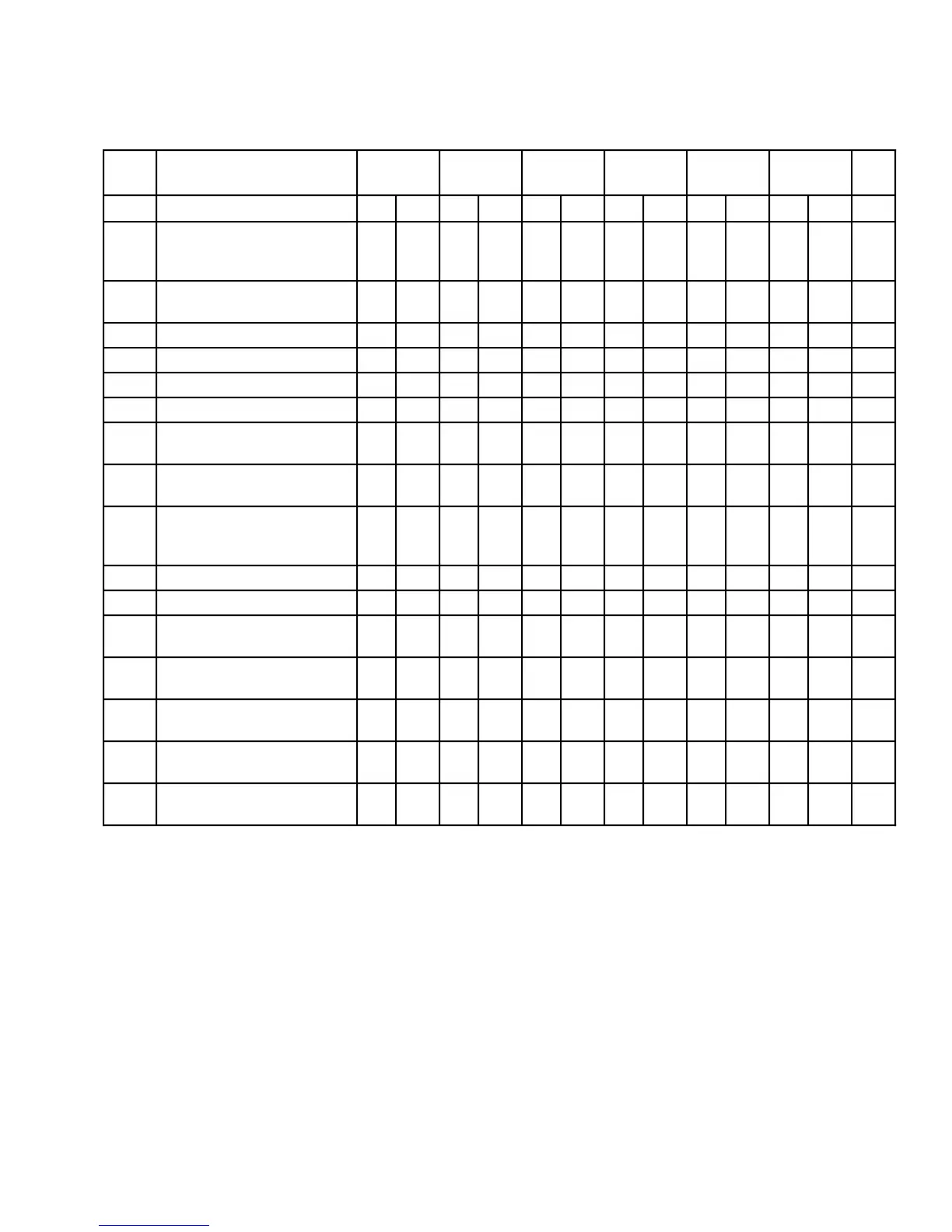

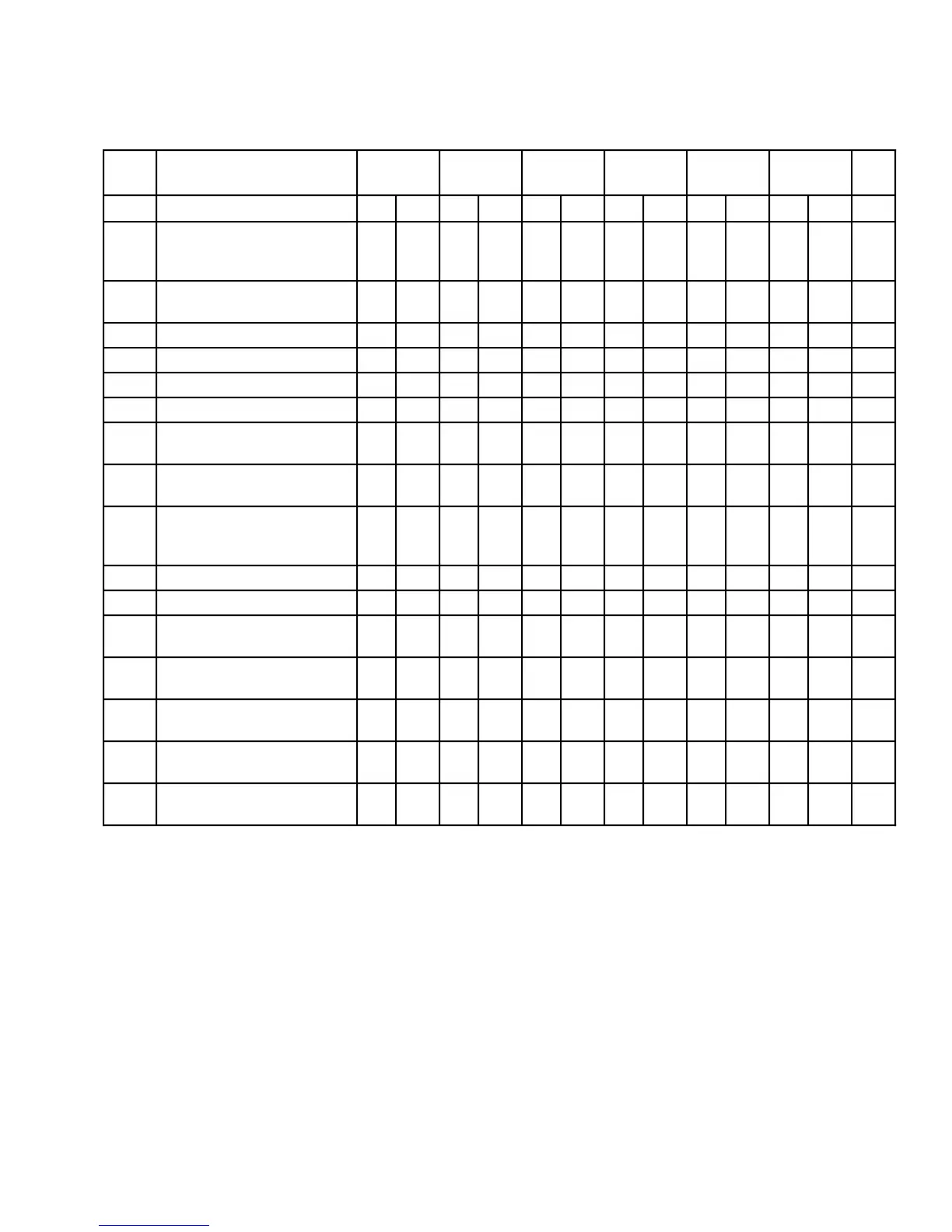

Num Characteristic 8 MHz* 10 MHz* 12.5 MHz*

16.67 MHz

12F

16 MHz 20 MHz

••

Unit

Min Max Min Max Min Max Min Max Min Max Min Max

7 Clock High to Address, Data

Bus High Impedance

(Maximum)

—80—70—60—50—50—42ns

16 Clock High to Control Bus

High Impedance

—80—70—60—50—50—42ns

33 Clock High to BG Asserted — 62 — 50 — 40 0 40 0 30 0 25 ns

34 Clock High to BG Negated — 62 — 50 — 40 0 40 0 30 0 25 ns

35 BR Asserted to BG Asserted 1.5 3.5 1.5 3.5 1.5 3.5 1.5 3.5 1.5 3.5 1.5 3.5 Clks

36

1

BR Negated to BG Negated 1.5 3.5 1.5 3.5 1.5 3.5 1.5 3.5 1.5 3.5 1.5 3.5 Clks

37 BGACK Asserted to BG

Negated

1.5 3.5 1.5 3.5 1.5 3.5 1.5 3.5 1.5 3.5 1.5 3.5 Clks

37A

2

BGACK Asserted to BR

Negated

20 1.5

Clks

20 1.5

Clks

20 1.5

Clks

10 1.5

Clks

10 1.5

Clks

10 1.5

Clks

Clks/

ns

38 BG Asserted to Control,

Address, Data Bus High

Impedance (AS Negated)

80 70 60 — 50 — 50 — 42 ns

39 BG Width Negated 1.5 — 1.5 — 1.5 — 1.5 — 1.5 — 1.5 — Clks

46 BGACK Width Low 1.5 — 1.5 — 1.5 — 1.5 — 1.5 — 1.5 — Clks

47 Asynchronous Input Setup

Time

10—10—10—5—5—5—ns

57 BGACK Negated to AS, DS,

R/ W Driven

1.5 — 1.5 — 1.5 — 1.5 — 1.5 — 1.5 — Clks

57A BGACK Negated to FC, VMA

Driven

1 — 1 — 1 — 1 — 1 — 1 — Clks

58

1

BR Negated to AS , DS, R/W

Driven

1.5 — 1.5 — 1.5 — 1.5 — 1.5 — 1.5 — Clks

58A

1

BR Negated to FC, VMA

Driven

1 — 1 — 1 — 1 — 1 — 1 — Clks

*These specifications represent improvement over previously published specifications for the 8-, 10-, and 12.5-MHz

MC68000 and are valid only for product bearing date codes of 8827 and later.

** Applies only to the MC68HC000 and MC68HC001.

NOTES:

1. Setup time for the synchronous inputs BGACK

, IPL0-IPL2 , and VPA guarantees their recognition at the

next falling edge of the clock.

2. BR need fall at this time only in order to insure being recognized at the end of the bus cycle.

3. Timing measurements are referenced to and from a low voltage of 0.8 volt and a high voltage of 2.0 volts,

unless otherwise noted. The voltage swing through this range should start outside and pass through the

range such that the rise or fall will be lienar between 0.8 volt and 2.0 volts.

4. The processor will negate BG and begin driving the bus again if external arbitration logic negates BR before

asserting BGACK.

5. The minimum value must be met to guarantee proper operation. If the maximum value is exceeded, BG may

be reasserted.

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...