3- 2 M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL MOTOROLA

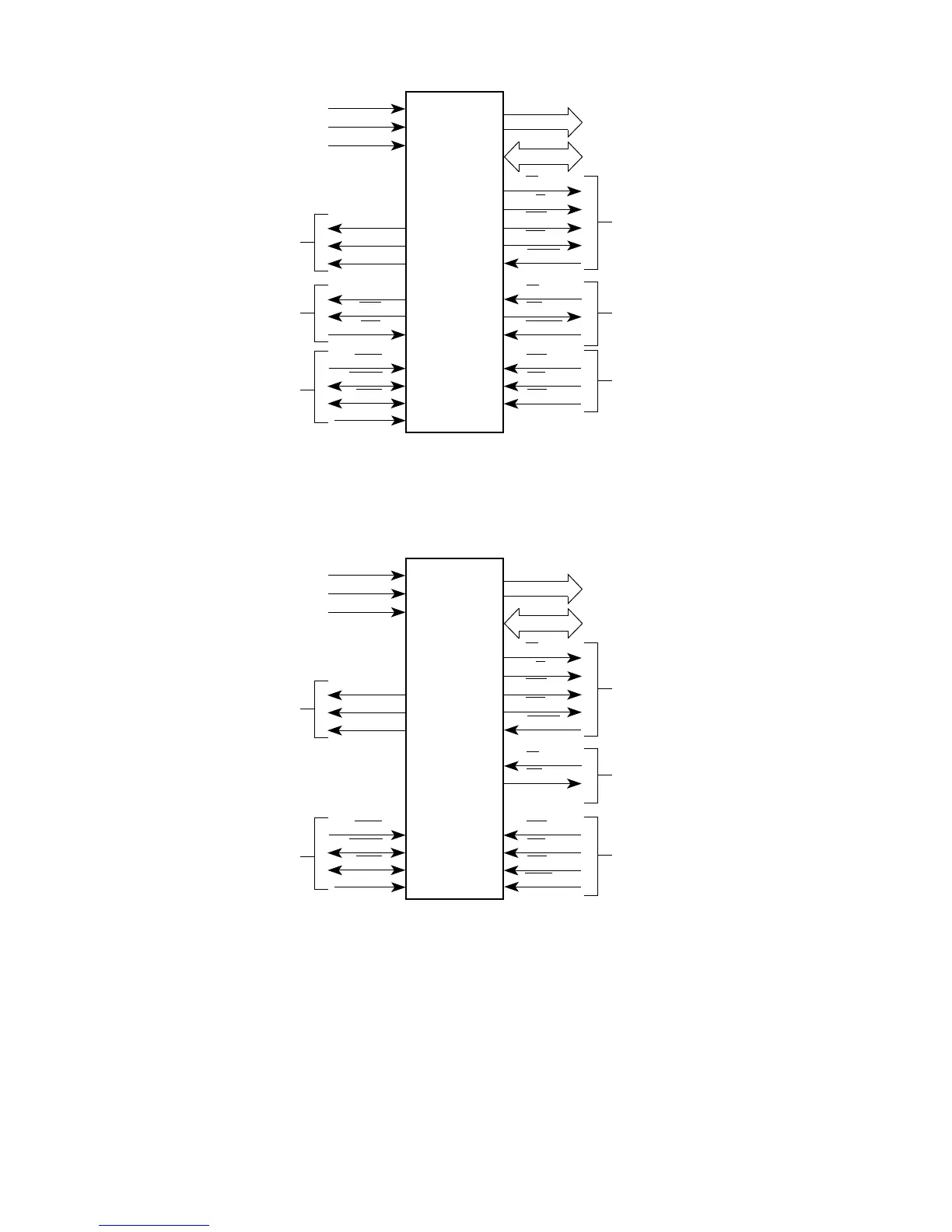

V

CC

(2)

GND(2)

CLK

ADDRESS

BUS

A23–A0

DATA BUS

D15–D0

AS

R/W

UDS

LDS

DTACK

ASYNCHRONOUS

BUS

CONTROL

BR

BG

BGACK

IPL1

IPL2

INTERRUPT

CONTROL

BUS

ARBITRATION

CONTROL

FC1

FC2

E

VMA

VPA

BERR

RESET

HALT

PROCESSOR

STATUS

MC6800

PERIPHERAL

CONTROL

SYSTEM

CONTROL

IPL0

FC0

MODE

Figure 3-2. Input and Output Signals

(MC68HC001)

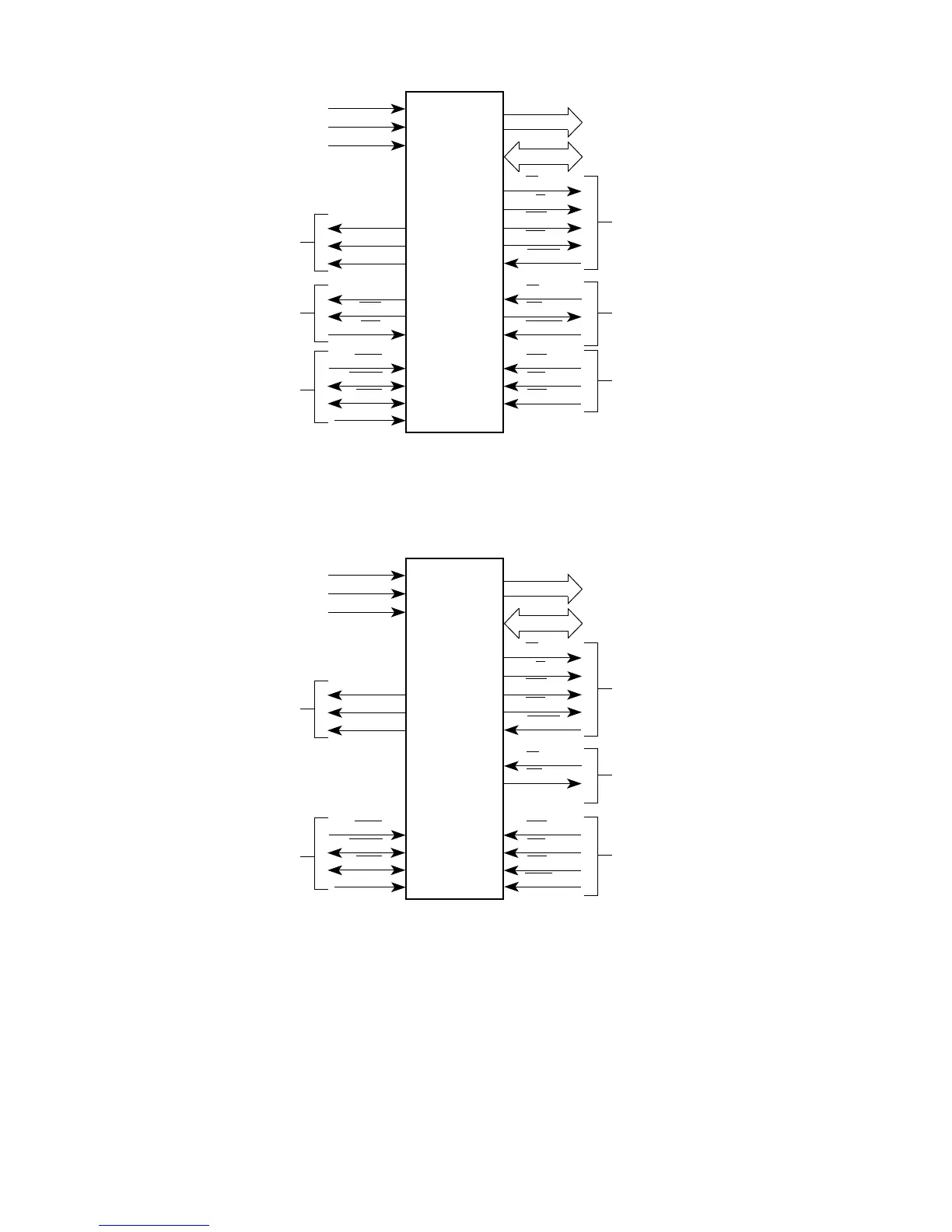

V

CC

(2)

GND(2)

CLK

ADDRESS

BUS

A23–A0

DATA BUS

D15–D0

AS

R/W

UDS

LDS

DTACK

ASYNCHRONOUS

BUS

CONTROL

BR

BG

IPL1

IPL2

INTERRUPT

CONTROL

BUS

ARBITRATION

CONTROL

FC1

FC2

BERR

RESET

HALT

PROCESSOR

STATUS

SYSTEM

CONTROL

IPL0

FC0

MODE

AVEC

MC68EC000

Figure 3-3. Input and Output Signals

(MC68EC000)

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...