MOTOROLA M68000 8-/16-/32-BIT MICROPROCESSOR USER’S MANUAL 2-3

tables. The SFC and DFC registers allow the supervisor to access user data space or

emulate CPU space cycles.

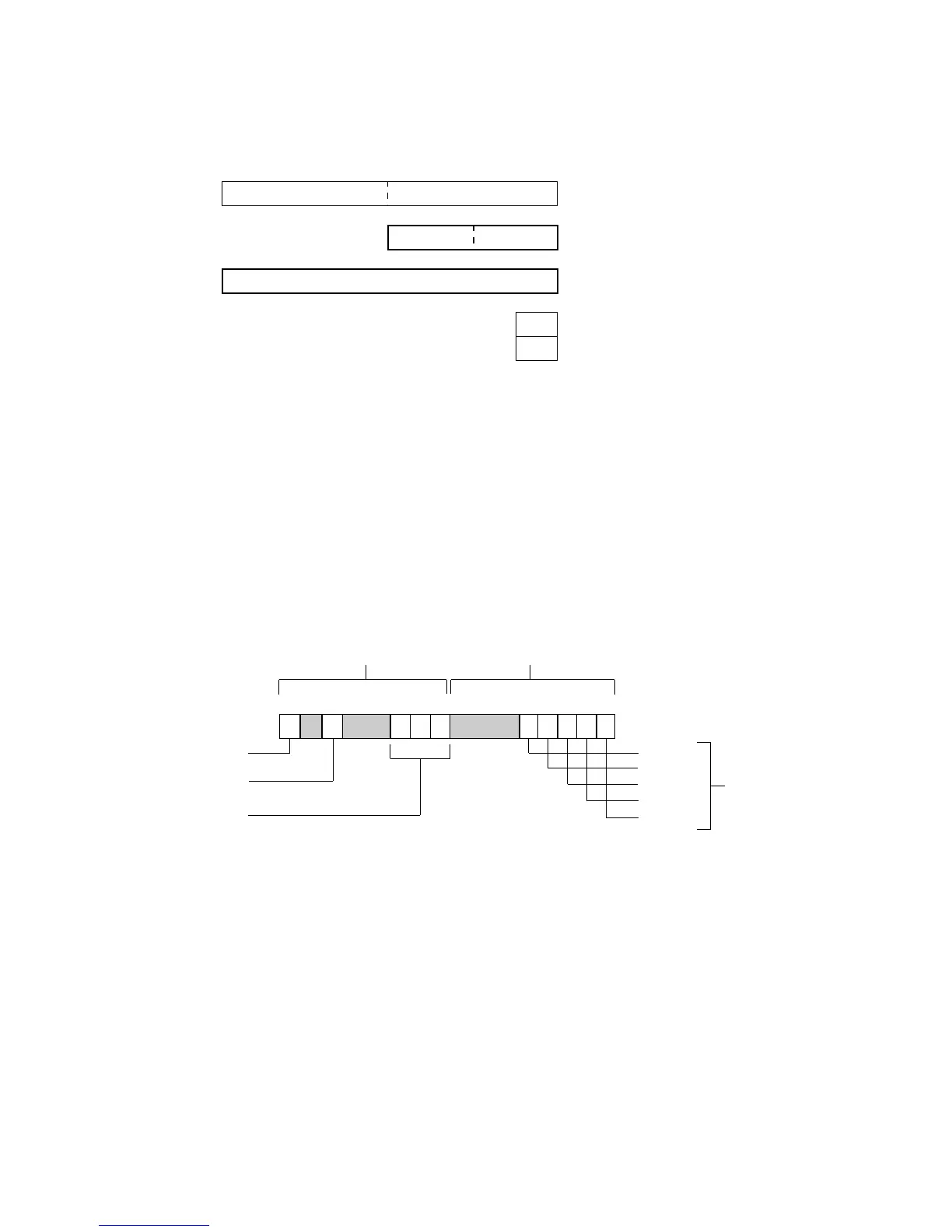

31 16 15 0

15 8 7 0

A7'

(SSP)

SUPERVISOR STACK

POINTER

CCR

SR STATUS REGISTER

31 0

VBR VECTOR BASE REGISTER

20

SFC

DFC

ALTERNATE FUNCTION

CODE REGISTERS

Figure 2-3. Supervisor Programmer's Model Supplement

(MC68010)

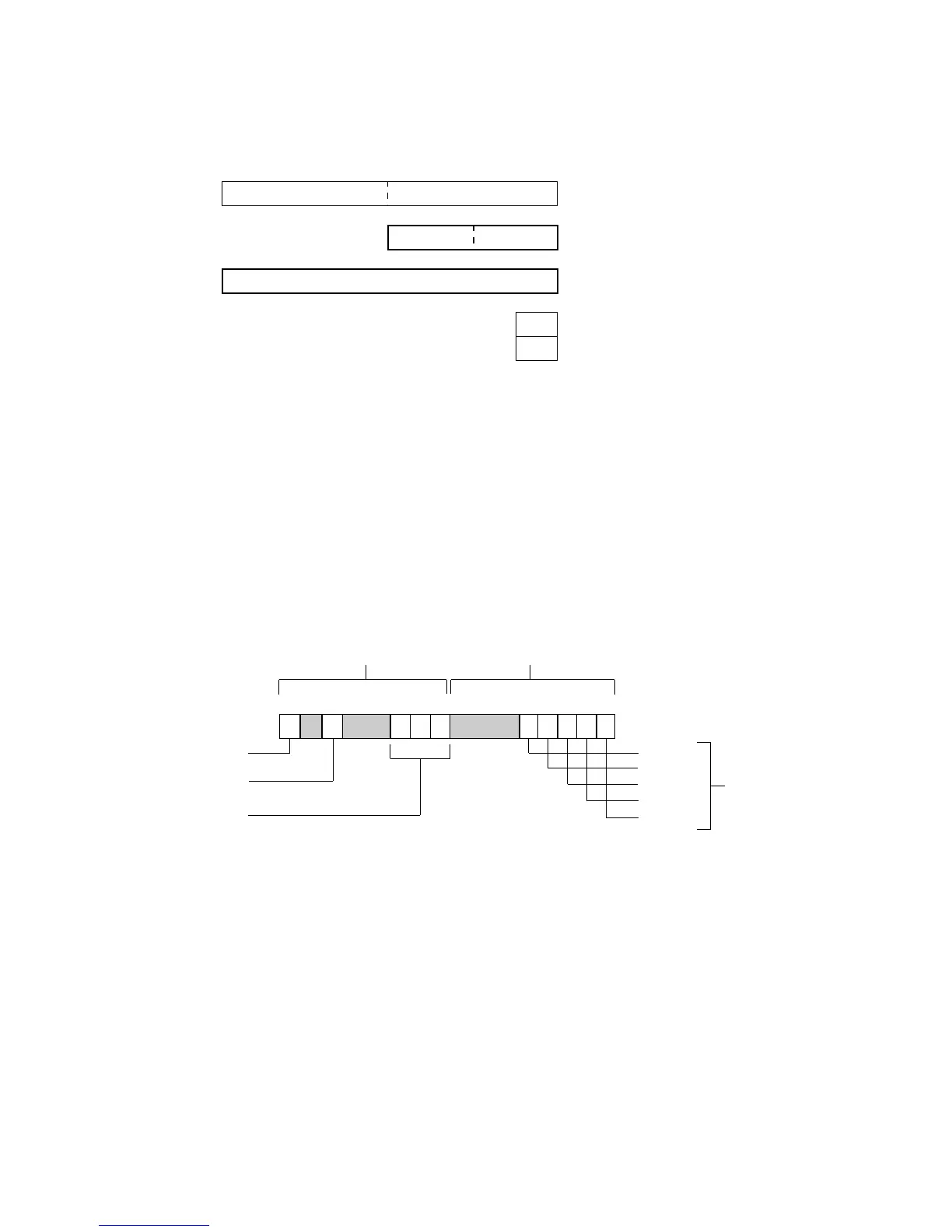

2.1.3 Status Register

The status register (SR),contains the interrupt mask (eight levels available) and the

following condition codes: overflow (V), zero (Z), negative (N), carry (C), and extend (X).

Additional status bits indicate that the processor is in the trace (T) mode and/or in the

supervisor (S) state (see Figure 2-4). Bits 5, 6, 7, 11, 12, and 14 are undefined and

reserved for future expansion

T

S

III

XNZVC

210

15 13 10 8 4 0

TRACE MODE

SUPERVISOR

STATE

INTERRUPT

MASK

EXTEND

NEGATIVE

ZERO

OVERFLOW

CARRY

CONDITION

CODES

SYSTEM BYTE USER BYTE

Figure 2-4. Status Register

2.2 DATA TYPES AND ADDRESSING MODES

The five basic data types supported are as follows:

1. Bits

2. Binary-Coded-Decimal (BCD) Digits (4 Bits)

3. Bytes (8 Bits)

4. Words (16 Bits)

5. Long Words (32 Bits)

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...