MOTOROLA M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL 5- 27

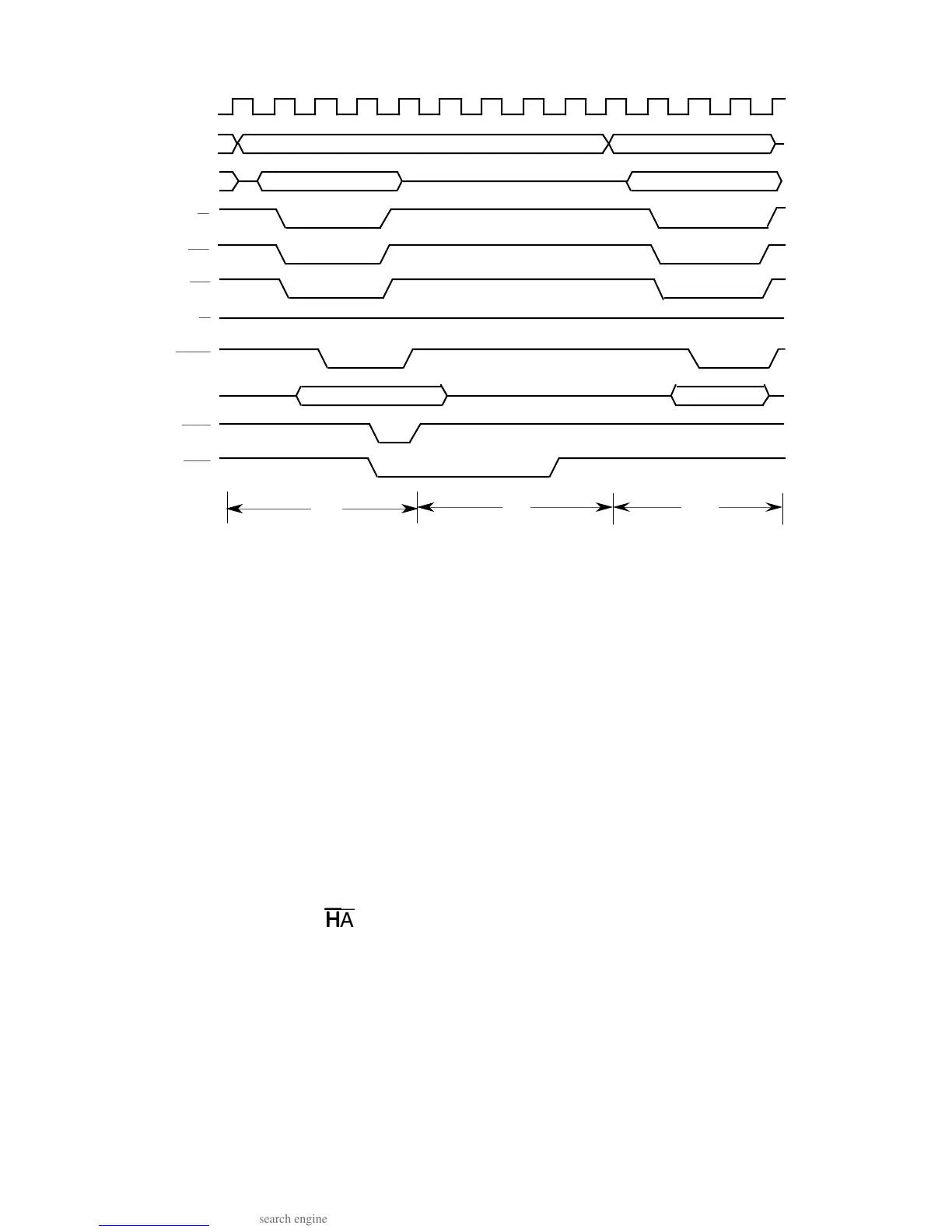

Figure 5-28. Delayed Retry Bus Cycle Timing Diagram

The processor terminates the bus cycle, then puts the address and data lines in the high-

impedance state. The processor remains in this state until HALT is negated. Then the

processor retries the preceding cycle using the same function codes, address, and data

(for a write operation). BERR should be negated at least one clock cycle before HALT is

negated.

NOTE

To guarantee that the entire read-modify-write cycle runs

correctly and that the write portion of the operation is

performed without negating the address strobe, the processor

does not retry a read-modify-write cycle. When a bus error

occurs during a read-modify-write operation, a bus error

operation is performed whether or not HALT is asserted.

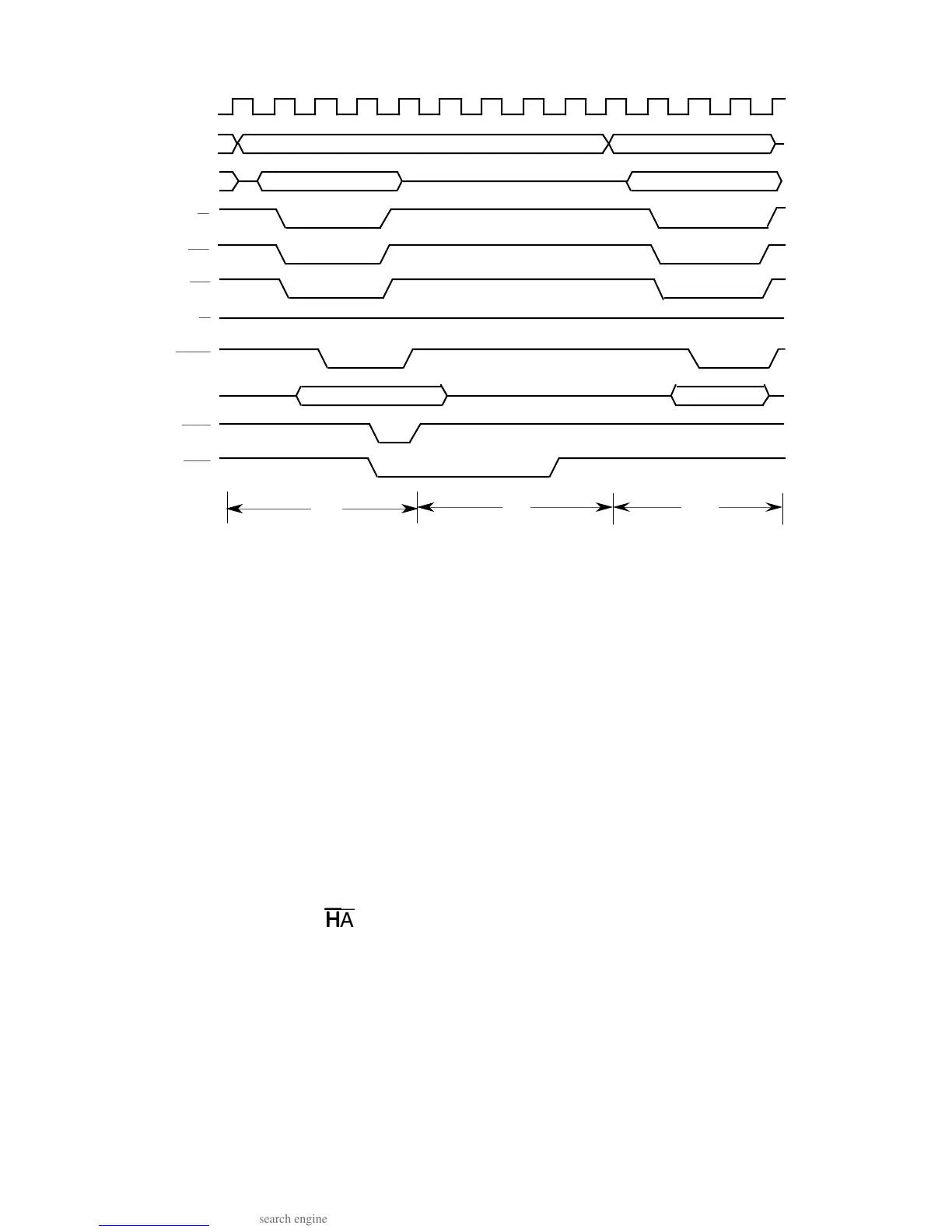

5.4.3 Halt Operation (

HALT performs a halt/run/single-step operation similar to the halt operation of an

MC68000. When HALT is asserted by an external device, the processor halts and remains

halted as long as the signal remains asserted, as shown in Figure 5-29.

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...