MOTOROLA M68000 8-/16-/32-BIT MICROPROCESSORS USER’S MANUAL 9- 7

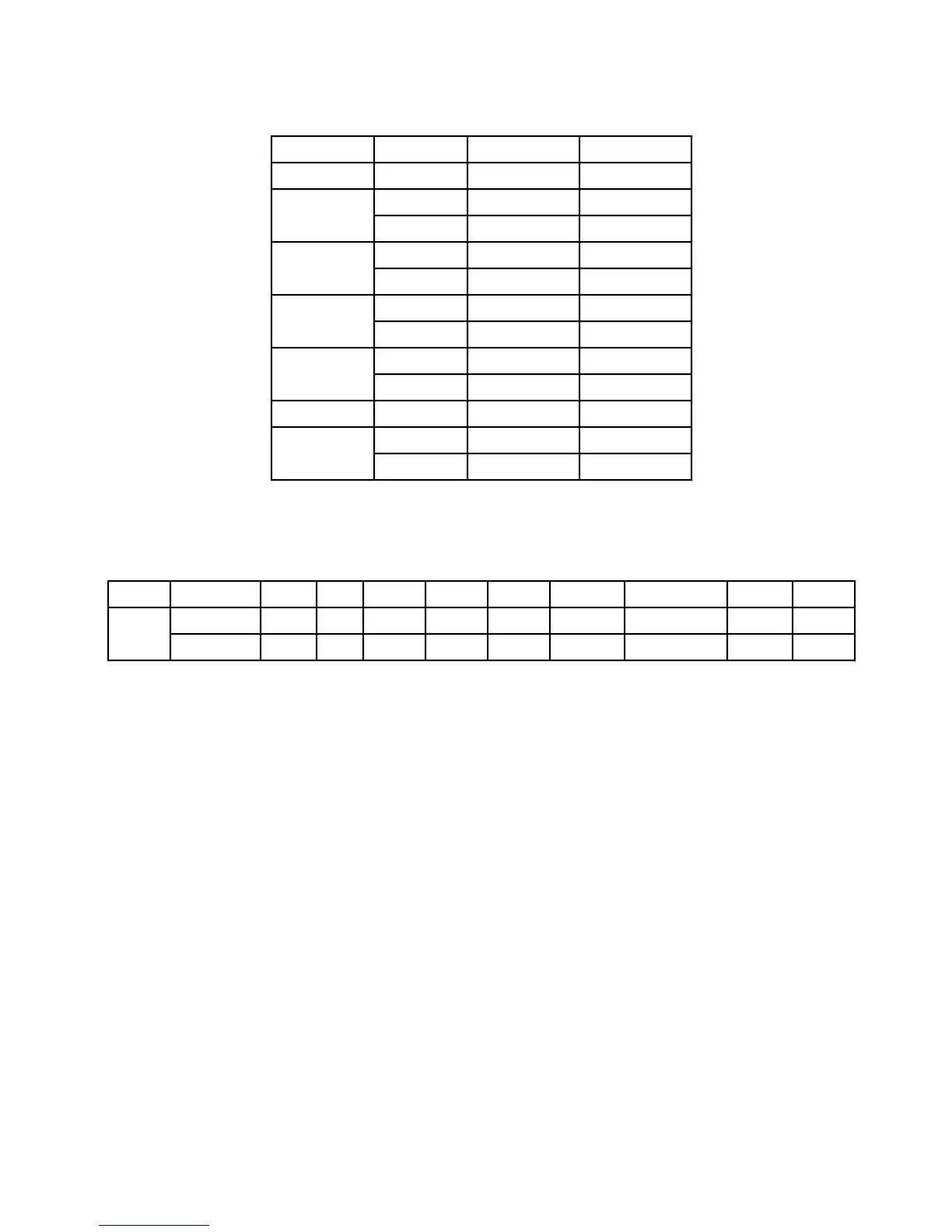

Table 9-9. Single Operand Instruction

Execution Times

Instruction Size Register Memory

NBCD Byte 6(1/0) 8(1/1)+

NEG Byte, Word 4(1/0) 8(1/1)+

Long 6(1/0) 12(1/2)+

NEGX Byte, Word 4(1/0) 8(1/1)+

Long 6(1/0) 12(1/2)+

NOT Byte, Word 4(1/0) 8(1/1)+

Long 6(1/0) 12(1/2)+

Scc Byte, False 4(1/0) 8(1/1)+*

Byte, True 4(1/0) 8(1/1)+*

TAS Byte 4(1/0) 14(2/1)+*

TST Byte, Word 4(1/0) 4(1/0)+

Long 4(1/0) 4(1/0)+

+Add effective address calculation time.

*Use nonfetching effective address calculation time.

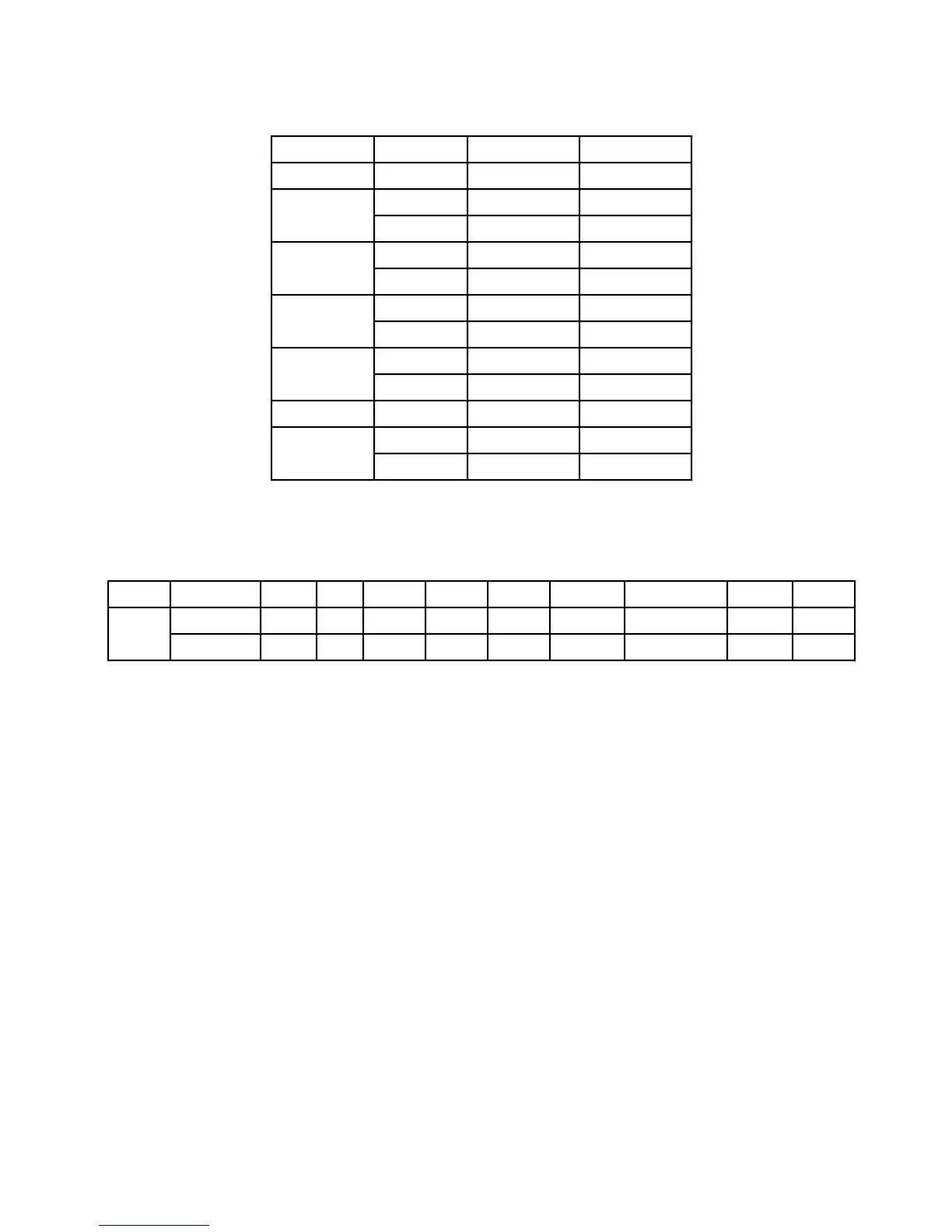

Table 9-10. Clear Instruction Execution Times

Size Dn An (An) (An)+ –(An) (d

16

, An) (d

8

, An, Xn)* (xxx).W (xxx).L

CLR Byte, Word 4(1/0) —8(1/1) 8(1/1) 10(1/1) 12(2/1) 16(2/1) 12(2/1) 16(3/1)

Long 6(1/0) —12(1/2) 12(1/2) 14(1/2) 16(2/2) 20(2/2) 16(2/2) 20(3/2)

*The size of the index register (Xn) does not affect execution time.

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...