MOTOROLA M68000 8-/16-/32-BIT MICROPROCESSORS USER’S MANUAL 9- 13

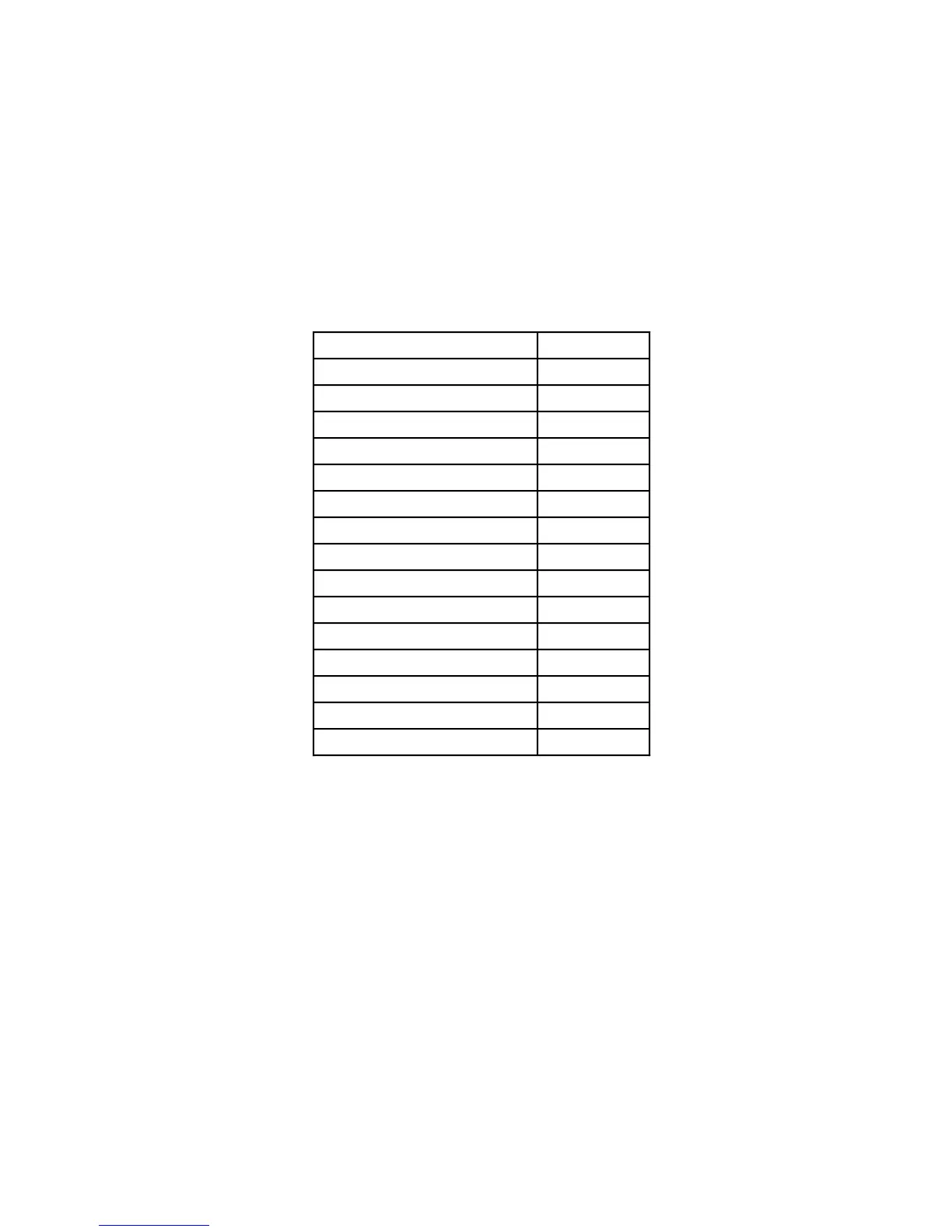

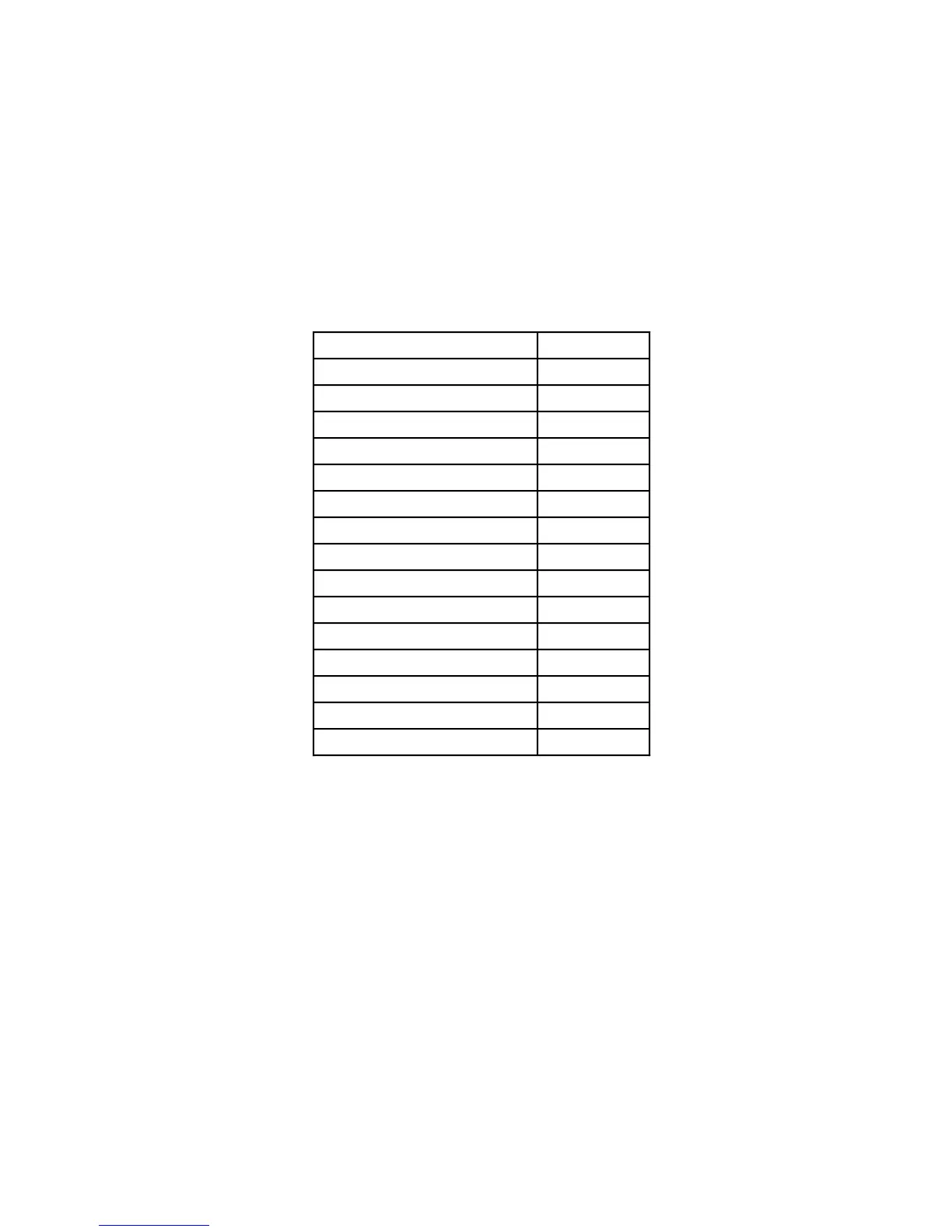

9.12 EXCEPTION PROCESSING EXECUTION TIMES

Table 9-19 lists the timing data for exception processing. The numbers of clock periods

include the times for all stacking, the vector fetch, and the fetch of the first instruction of

the handler routine. The total number of clock periods, the number of read cycles, and the

number of write cycles are shown in the previously described format. The number of clock

periods, the number of read cycles, and the number of write cycles, respectively, must be

added to those of the effective address calculation where indicated by a plus sign (+).

Table 9-19. Exception Processing

Execution Times

Exception

Address Error 126(4/26)

Breakpoint Instruction* 45(5/4)

Bus Error 126(4/26)

CHK Instruction** 44(5/4)+

Divide By Zero 42(5/4)+

Illegal Instruction 38(5/4)

Interrupt* 46(5/4)

MOVEC, Illegal Control Register** 46(5/4)

Privilege Violation 38(5/4)

Reset*** 40(6/0)

RTE, Illegal Format 50(7/4)

RTE, Illegal Revision 70(12/4)

Trace 38(4/4)

TRAP Instruction 38(4/4)

TRAPV Instruction 38(5/4)

+ Add effective address calculation time.

* The interrupt acknowledge and breakpoint cycles

are assumed to take four clock periods.

** Indicates maximum value.

*** Indicates the time from when RESET and HALT

are first sampled as negated to when instruction

execution starts.

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...