MOTOROLA M68000 8-/16-/32-BIT MICROPROCESSOR USER’S MANUAL 2-11

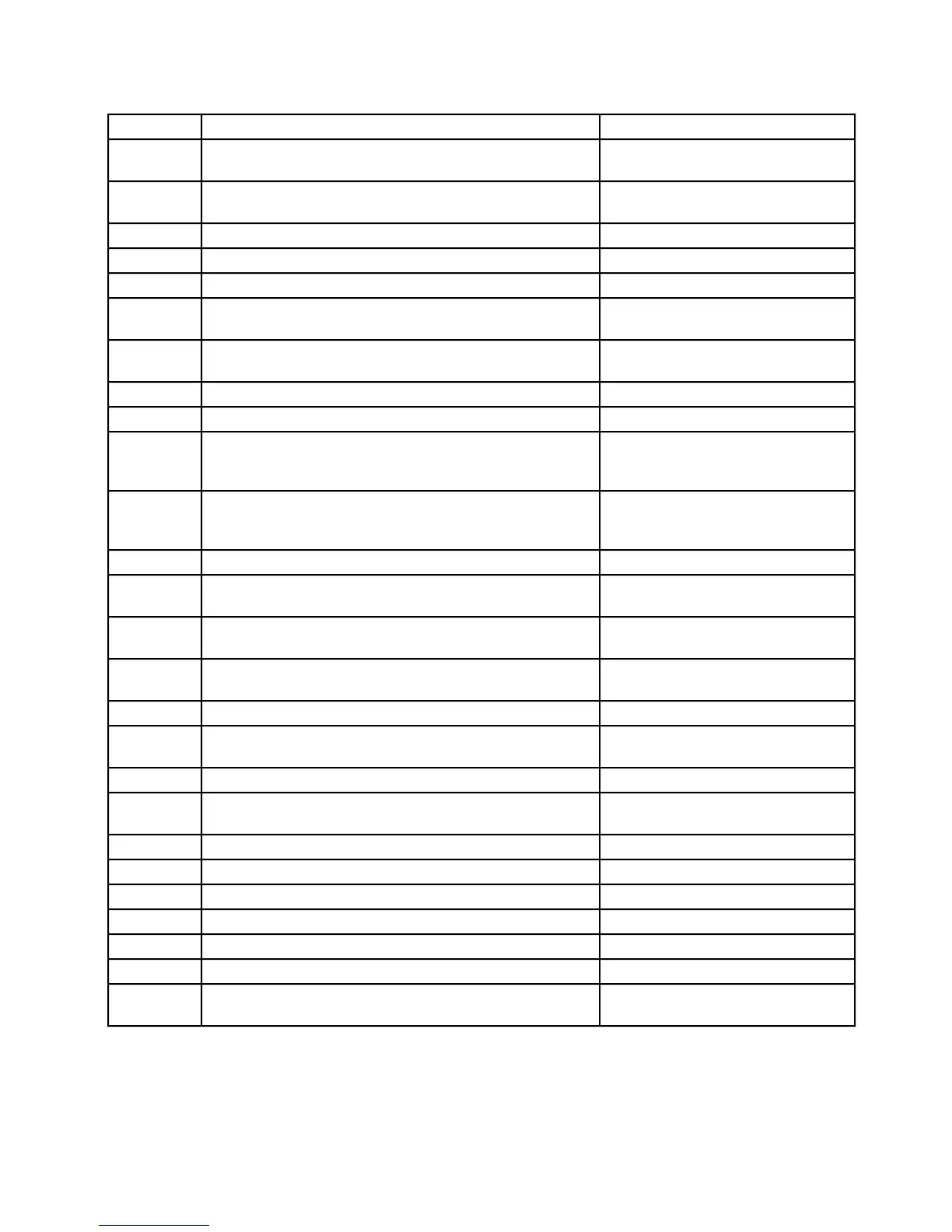

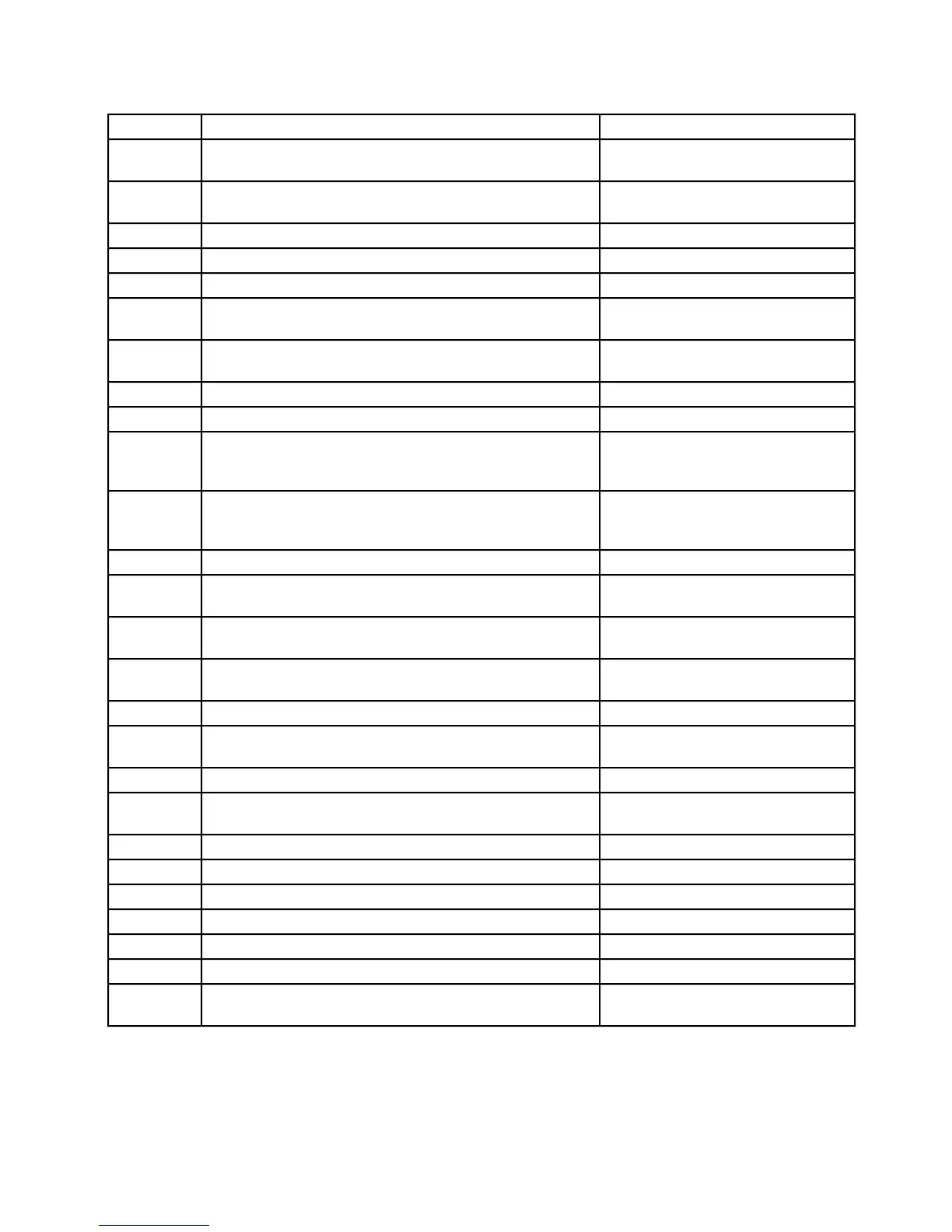

Table 2-2. Instruction Set Summary (Sheet 1 of 4)

Opcode Operation Syntax

ABCD Source

10

+ Destination

10

+ X → Destination ABCD Dy,Dx

ABCD –(Ay), –(Ax)

ADD Source + Destination → Destination ADD <ea>,Dn

ADD Dn,<ea>

ADDA Source + Destination → Destination ADDA <ea>,An

ADDI Immediate Data + Destination → Destination ADDI # <data>,<ea>

ADDQ Immediate Data + Destination → Destination ADDQ # <data>,<ea>

ADDX Source + Destination + X → Destination ADDX Dy, Dx

ADDX –(Ay), –(Ax)

AND Source Λ Destination → Destination AND <ea>,Dn

AND Dn,<ea>

ANDI Immediate Data Λ Destination → Destination ANDI # <data>, <ea>

ANDI to CCR Source Λ CCR → CCR ANDI # <data>, CCR

ANDI to SR If supervisor state

then Source Λ SR → SR

else TRAP

ANDI # <data>, SR

ASL, ASR Destination Shifted by <count> → Destination ASd Dx,Dy

ASd # <data>,Dy

ASd <ea>

Bcc If (condition true) then PC + d → PC Bcc <label>

BCHG ~ (<number> of Destination) → Z;

~ (<number> of Destination) → <bit number> of Destination

BCHG Dn,<ea>

BCHG # <data>,<ea>

BCLR ~ (<bit number> of Destination) → Z;

0 → <bit number> of Destination

BCLR Dn,<ea>

BCLR # <data>,<ea>

BKPT Run breakpoint acknowledge cycle;

TRAP as illegal instruction

BKPT # <data>

BRA PC + d → PC BRA <label>

BSET ~ (<bit number> of Destination) → Z;

1 → <bit number> of Destination

BSET Dn,<ea>

BSET # <data>,<ea>

BSR SP – 4 → SP; PC → (SP); PC + d → PC BSR <label>

BTST – (<bit number> of Destination) → Z; BTST Dn,<ea>

BTST # <data>,<ea>

CHK If Dn < 0 or Dn > Source then TRAP CHK <ea>,Dn

CLR 0 → Destination CLR <ea>

CMP Destination—Source → cc CMP <ea>,Dn

CMPA Destination—Source CMPA <ea>,An

CMPI Destination —Immediate Data CMPI # <data>,<ea>

CMPM Destination—Source → cc CMPM (Ay)+, (Ax)+

DBcc If condition false then (Dn – 1 → Dn;

If Dn ≠ –1 then PC + d → PC)

DBcc Dn,<label>

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...