5- 38 M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL MOTOROLA

.

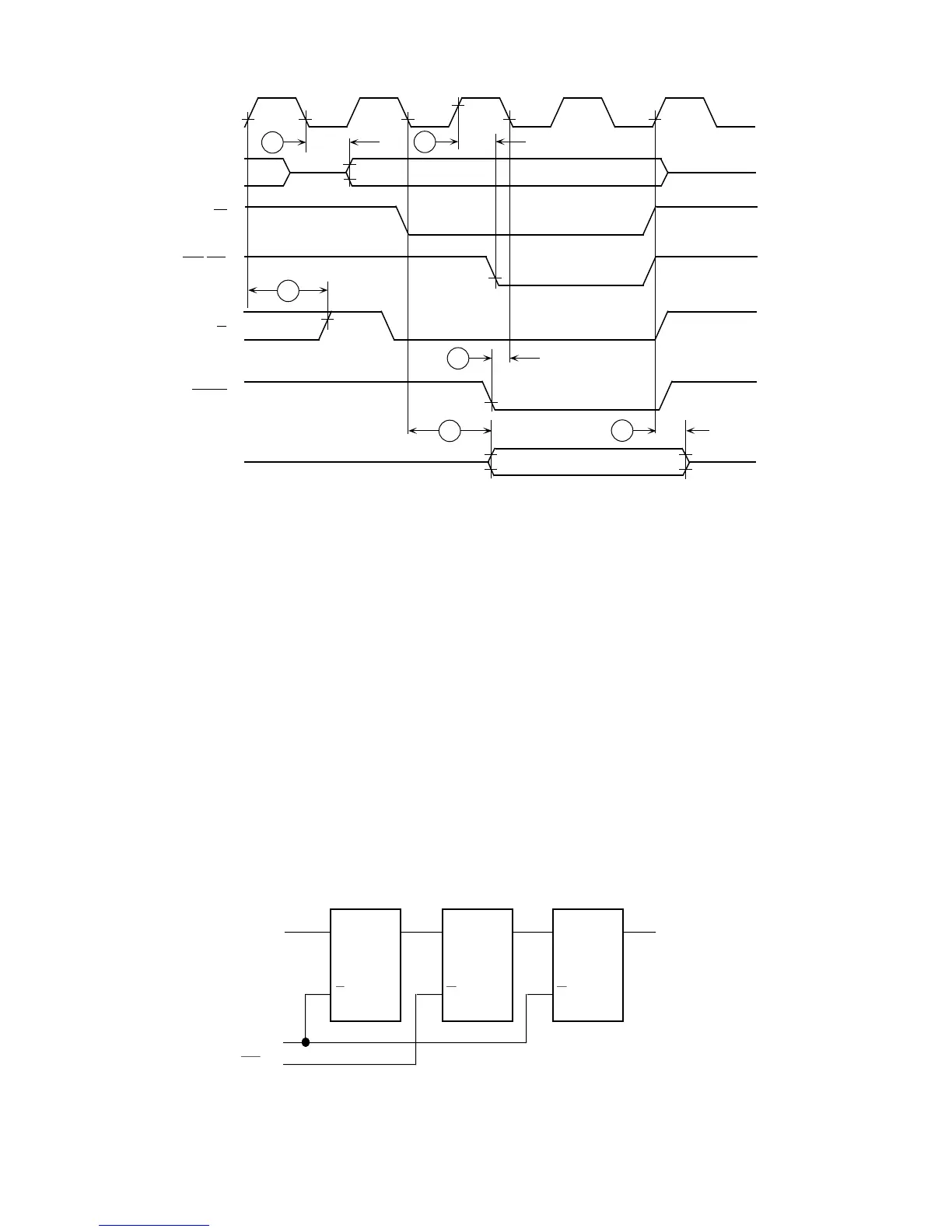

ADDR

UDS/LDS

R/W

AS

CLOCK

DTACK

6

S0 S1 S2 S3 S4 S5 S6 S7 S0

18

DATA

23 53

47

9

Figure 5-36. Synchronous Write Cycle

A key consideration when designing in a synchronous environment is the timing for the

assertion of DTACK and BERR by an external device. To properly use external inputs, the

processor must synchronize these signals to the internal clock. The processor must

sample the external signal, which has no defined phase relationship to the CPU clock,

which may be changing at sampling time, and must determine whether to consider the

signal high or low during the succeeding clock period. Successful synchronization requires

that the internal machine receives a valid logic level (not a metastable signal), whether the

input is high, low, or in transition. Metastable signals propagating through synchronous

machines can produce unpredictable operation.

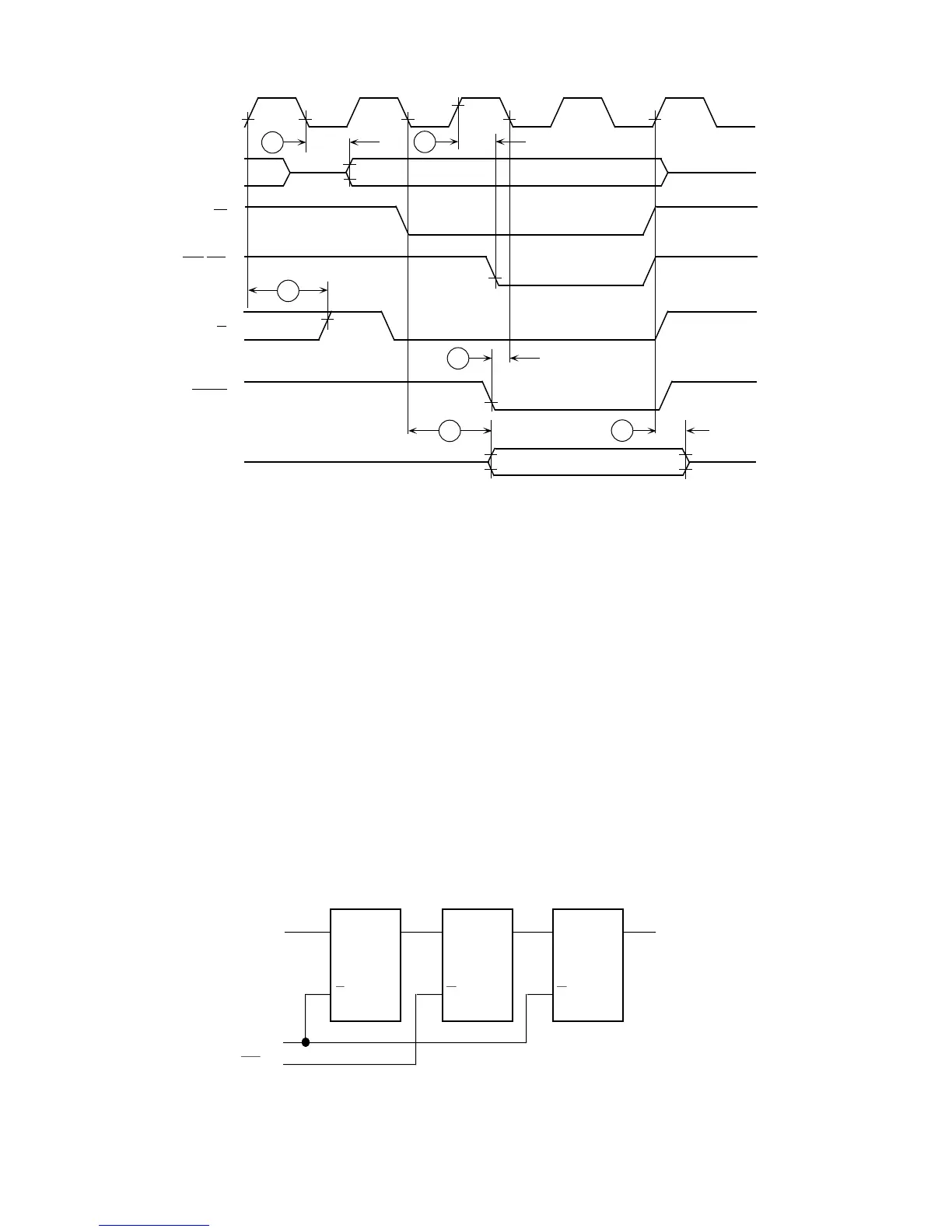

Figure 5-37 is a conceptual representation of the input synchronizers used by the M68000

Family processors. The input latches allow the input to propagate through to the output

when E is high. When low, E latches the input. The three latches require one cycle of CLK

to synchronize an external signal. The high-gain characteristics of the devices comprising

the latches quickly resolve a marginal signal into a valid state.

IGNA

IGNA

Figure 5-37. Input Synchronizers

Frees

cale Semiconductor,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...