NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 12

CARRIER_PWR_ON signal is generated by the module and passed to the Carrier Board to indicate that the module is powered

up and that the pow er up sequence for the Carrier Board circuits can begin.

RESET_OUT# is de-asserted by the Carrier Board after a period sufficient to allow the Carrier Board circuits to pow er up.

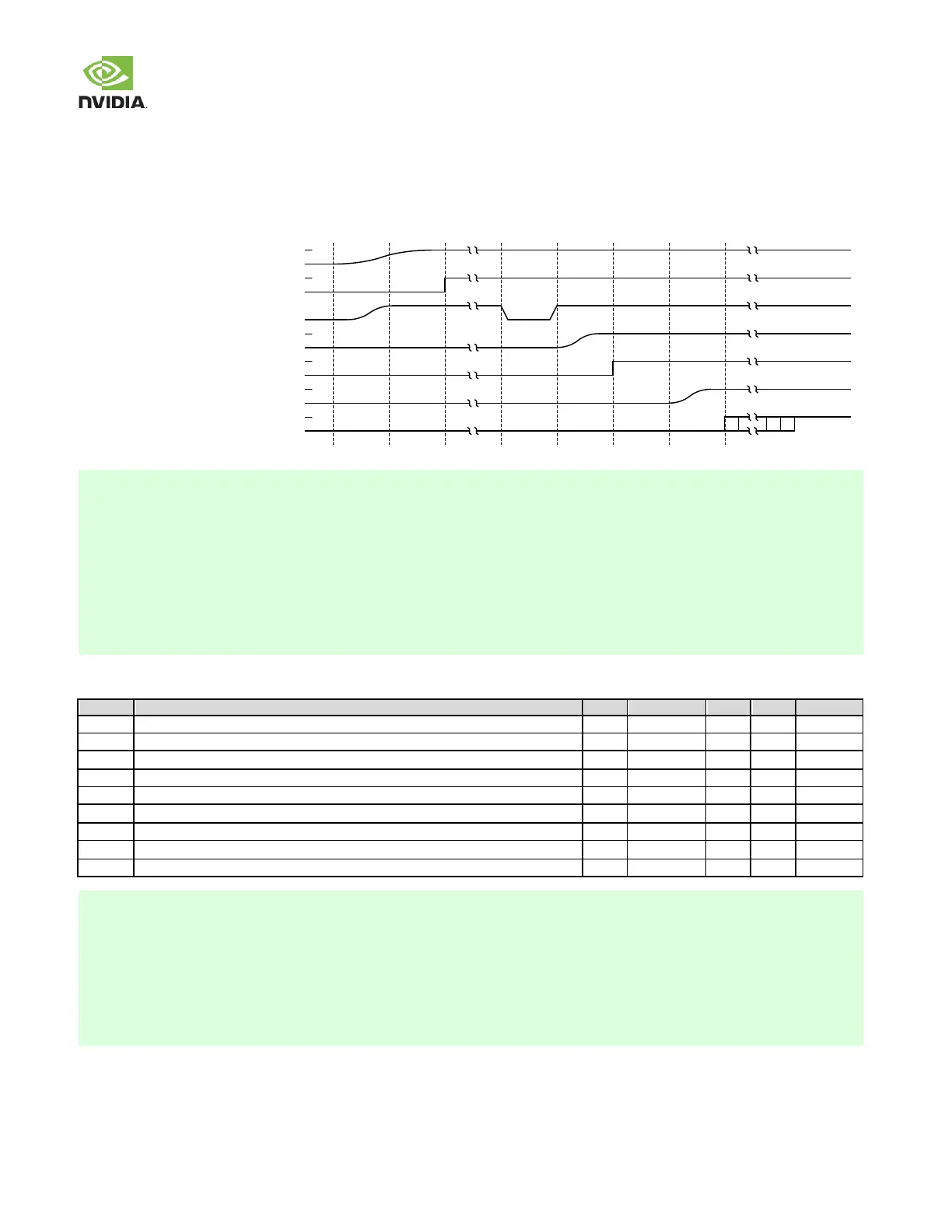

Figure 3. Power Up Sequence – Power-Button Case (Jetson TX2i in P2597_C02)

CARRIER_PWR_ON

POWER_BTN#

VIN_PWR_BAD#

VDD_IN

Carrier Board VDD_1V8 (note 1)

Jetson module System Power (Main 1.8V

rail most IF pins are associated with)

1 2 3 4 5 6 7

RESET_OUT# (note 2)

8

1. The 1.8V supply on the carrier board associated with MPIO pins common to the module must not be enabled unless the

module main 1.8V rail is on. In addition, the carrier board should keep RESET_OUT# low until this 1.8V supply is valid.

On the P2597, this is accomplished by connecting the VDD_1V8 supply PGOOD signal to RESET_OUT#.

2. Inactive when both PMIC Reset is inactive (high) & VDD_1V8 PGOOD is active (high)

3. During run time if any module I/O rail is switched OFF or ON, the following sequences should be performed. Violating

these sequences will result in extra in-rush current during the rail transition.

- OFF Sequence: The associated NO_IOPOWER bit in the PMC APBDEV_PMC_NO_IOPOWER_0 register must be enabled before the

I/O Rail is powered OFF

- ON Sequence. After an I/O Rail is powered ON, the associated NO_IOPOWER bit in the PMC APBDEV_PMC_NO_IOPOWER_0

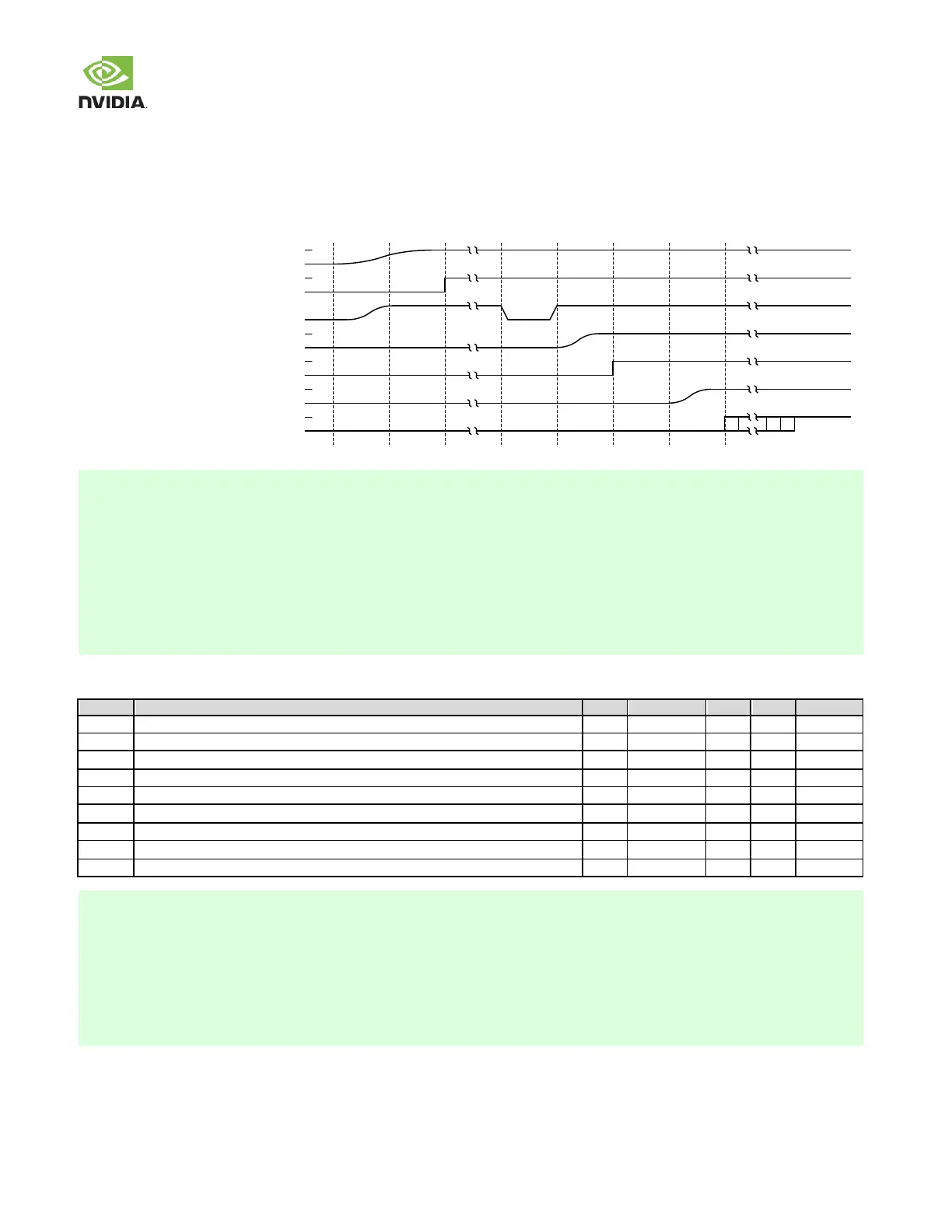

Table 7. Power Up Sequence Timing Relationships

VDD_IN On to POWER_BTN# Pull-up (PMIC) active

VDD_IN On to VIN_PWR_BAD# inactive

VIN_PWR_BAD# inactive to POWER_BTN# active

POWER_BTN# active to CARRIER_PWR_ON active

Module System Power On to CARRIER_PWR_ON

CARRIER_PWR_ON active to Carrier Board System Power Enabled

CARRIER_PWR_ON to On-Module PMIC Reset Inactive

1. Measured from VDD_IN ramp start to POWER_BTN# ramp start. Carrier board dependent.

2. Typical value using NVIDIA P2597, measured from VDD_IN ramp start to VIN_PWR_BAD# inactive start. Carrier board

dependent.

3. User Dependent if POWER_BTN# connected to button. Otherwise, carrier board dependent.

4. Typical value measured using NVIDIA P2597. Carrier board dependent

5. Typical value using P2597. Carrier board dependent.

6. User Dependent if RESET_IN# connected to button. Otherwise, carrier board dependent. Not shown in Power up

sequence figure.

Loading...

Loading...