NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 80

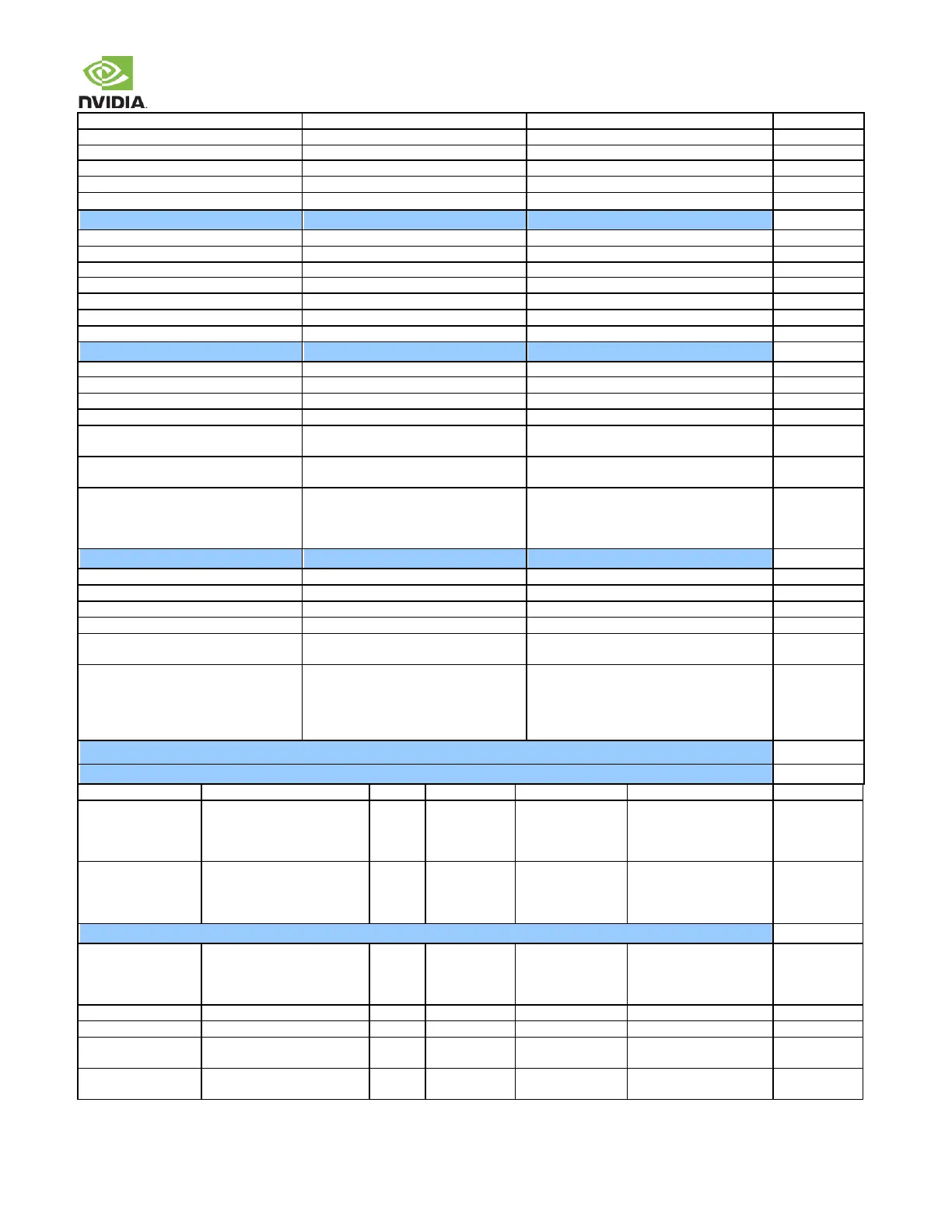

0.1uF capacitors if directly connected

0.1uF capacitors if directly connected

1.8V to 3.3V Level Shifter

Magnetics near RJ45 connector

Magnetics near RJ45 connector

Magnetics near RJ45 connector

Magnetics near RJ45 connector

LED and pull-up Current Limiting Circuit

LED and pull-up Current Limiting Circuit

LED and pull-up Current Limiting Circuit

-down to GND near connector

(DP only)

100k-up to 3.3V near connector (DP

only)

10k-up to 1.8V near main conn. &

-down to GND on DP side of

level shifter.

Level Shifter (w/output toward main

connector) near main connector & 100k

resistor to DP connector. Level shifter must be

non-inverting.

499 GND

499 GND

499 GND

499 GND

10k-up to 3.3V near main conn. &

-up to 5V near HDMI conn.

Bidirectional level shifter between Pull-ups in

Parallel Termination column

10k-up to 1.8V near main conn. &

-down to GND near HDMI conn.

Level shifter (w/output toward main connector)

between Pull-up & Pull-down in Parallel

Termination column. Level shifter can be

inverting or non-inverting.

resistor between pull-down & HDMI connector.

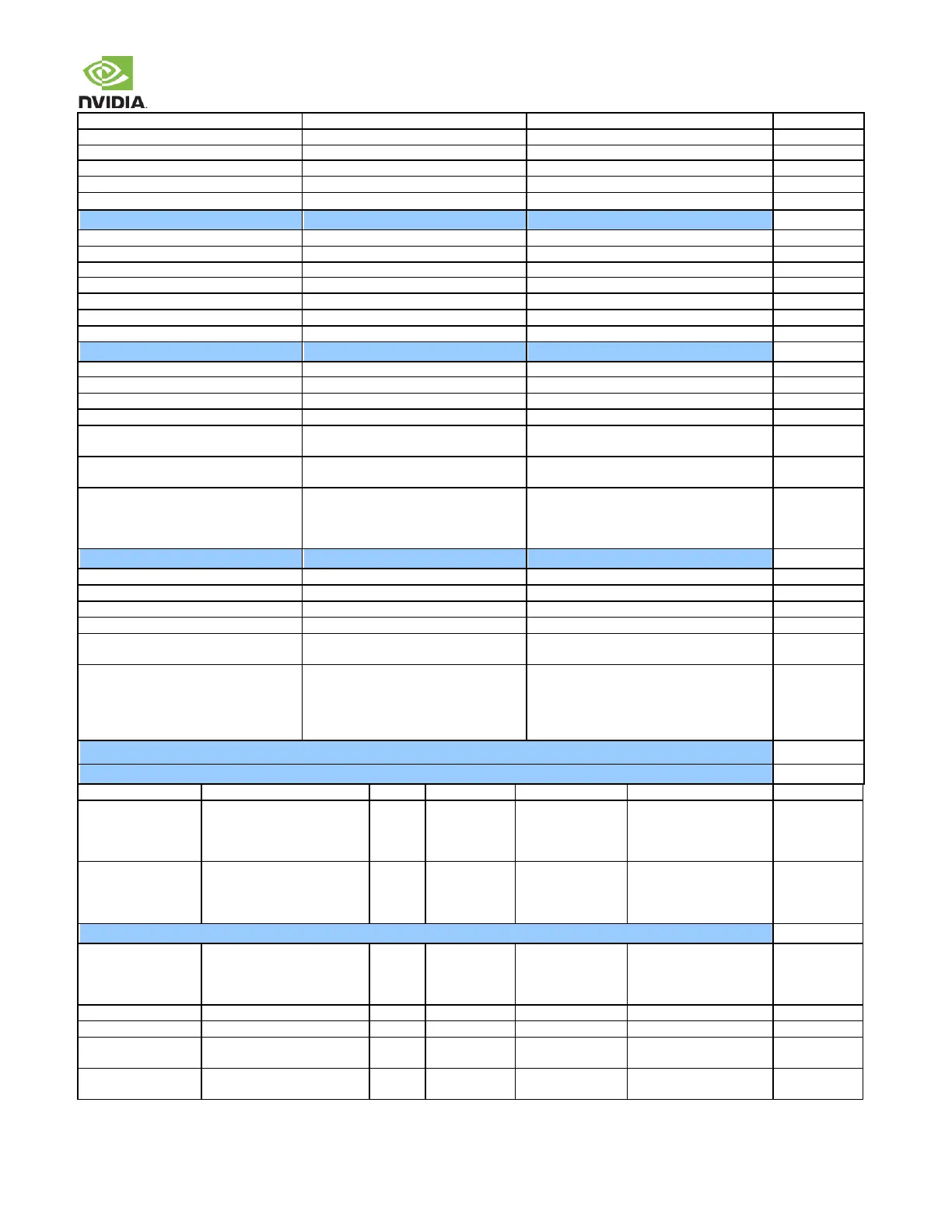

TX2: 5.5-

19.6

TX2i:

9.0-19.0

PMIC is supply

when charging

cap or coin cell

Super cap or coin

cell is source when

system power

removed

Main power input from DC

Adapter

TX2: 5.5-

19.6

TX2i:

9.0-19.0

1V8_IO_VREG_EN

(VDD_3V3_SYS_PG)

3.3V rail, off in Sleep (various)

Loading...

Loading...