NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 96

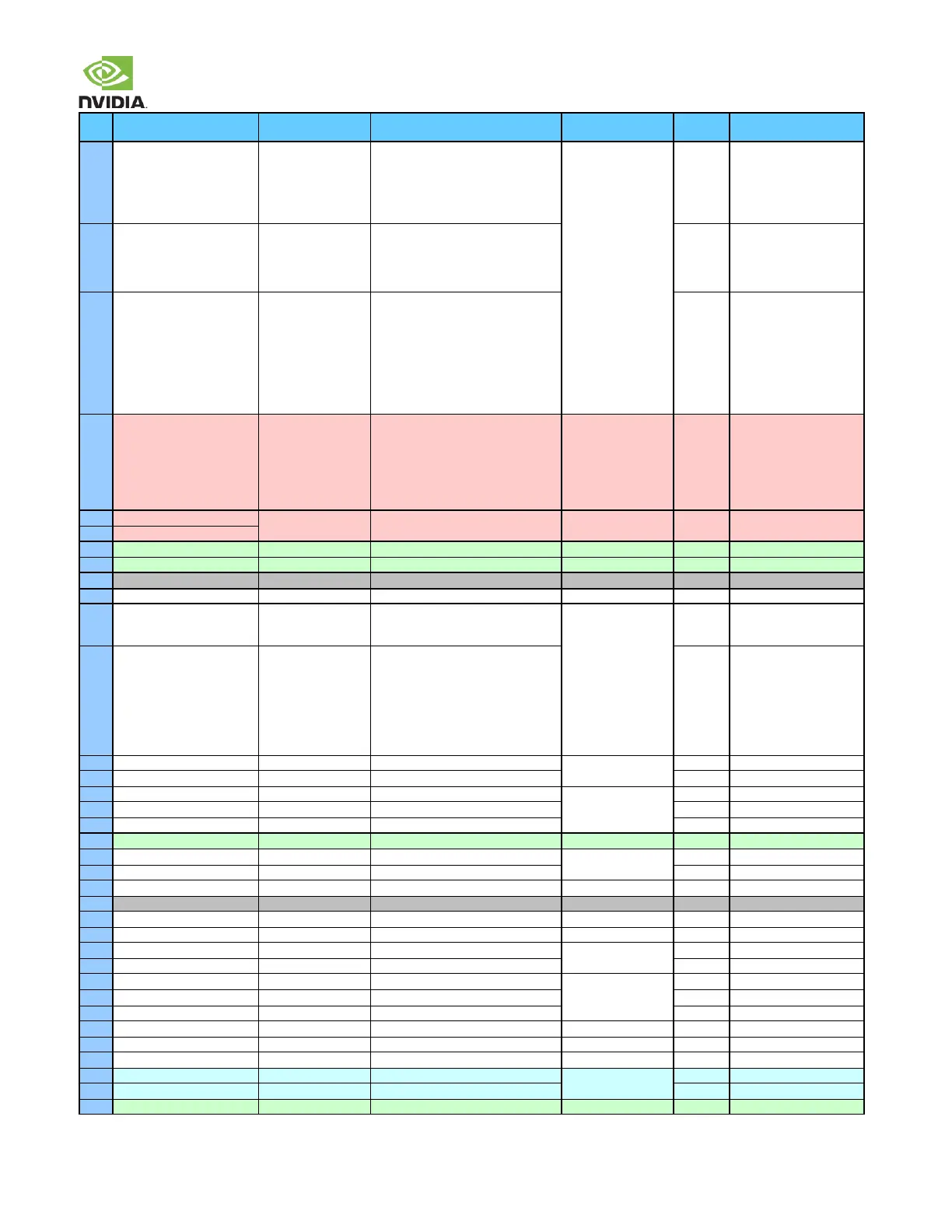

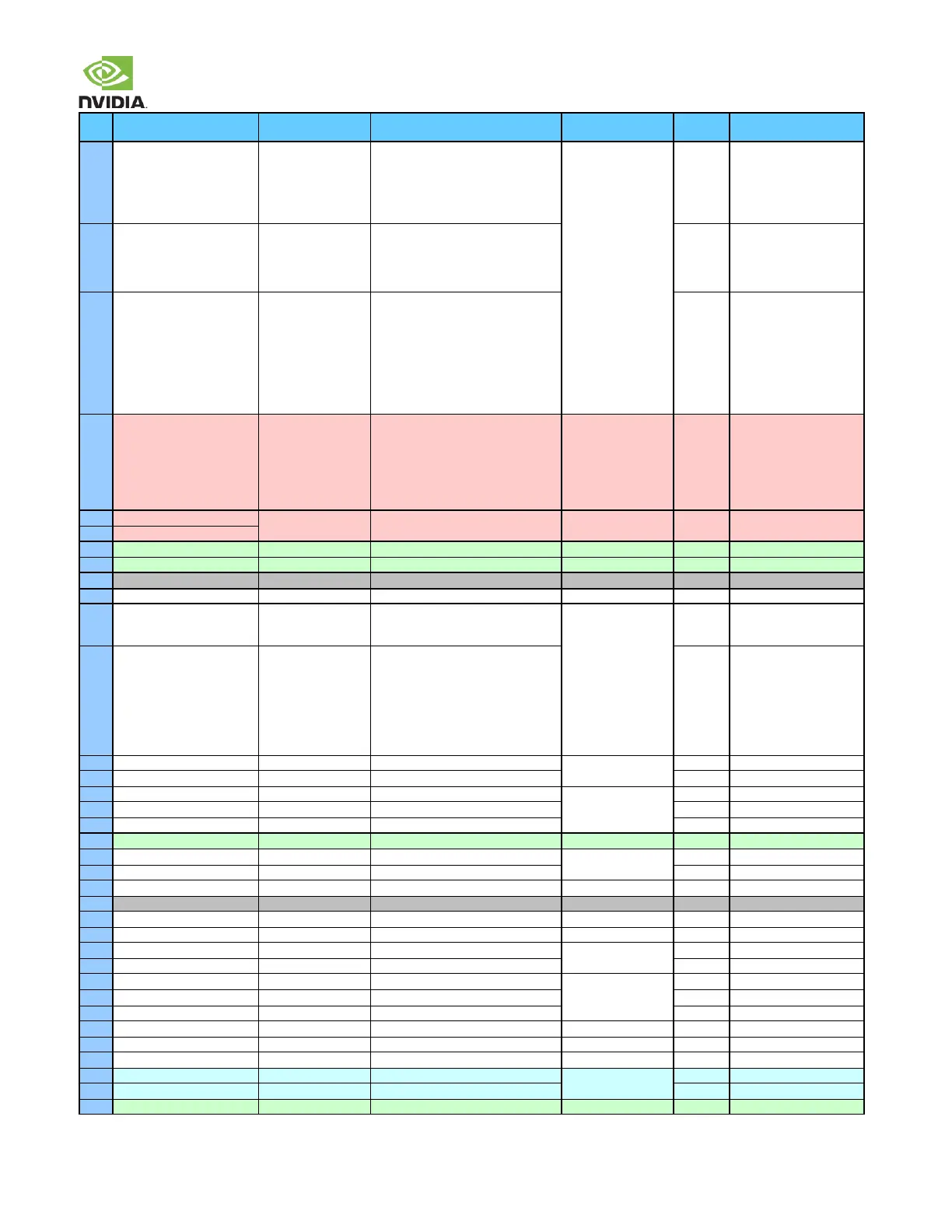

Usage on the Carrier

Board

Reset In. System Reset driven from

PMIC to carrier board for devices

requiring full system reset. Also driven

from carrier board to initiate full system

reset (i.e. RESET button). A pull-up is

present on module.

Carrier Power On. Used as part of the

power up sequence. The module asserts

this signal when it is safe for the carrier

-up to

VDD_3V3_SYS is present on the module.

Charger Present. Connected on module

-up

internally to MBATT (VDD_5V0_SYS).

Can optionally be used to support auto-

power-on where the module platform

will power-on when the main power

source is connected instead of waiting

for a power button press.

MBATT level 5.0V (see

note 3)

Real-Time-Clock. Optionally used to

provide back-up power for RTC.

Connects to Lithium Cell or super

capacitor on Carrier Board. PMIC is

supply when charging cap or coin cell.

Super cap or coin cell is source when

system is disconnected from power.

Battery Back-up using

Super-capacitor

Main power Supplies PMIC & external

supplies

5.5V-19.6V (TX2)

9.0V-19.0V (TX2i)

Carrier Board Standby: The module

drives this signal low when it is in the

standby power state.

VDD_IN Power Bad. Carrier board

indication to the module that the

VDD_IN power is not valid. Carrier board

should de-assert this (drive high) only

when VDD_IN has reached its required

voltage level and is stable. This prevents

Tegra from powering up until the

VDD_IN power is stable.

Modem to AP (Tegra) Ready or GPIO

JTAG Header & Debug

Connector

JTAG General Purpose 0 (Test Reset)

AP (Tegra) Wake Bluetooth or GPIO

WLAN 2 Wake AP (Tegra) or GPIO

BT 2 Wake AP (Tegra) or GPIO

Loading...

Loading...