NVIDIA Jetson TX2/TX2i OEM Product Design Guide

JETSON TX2/TX2i OEM PRODUCT | DESIGN GUIDE | 20180618 97

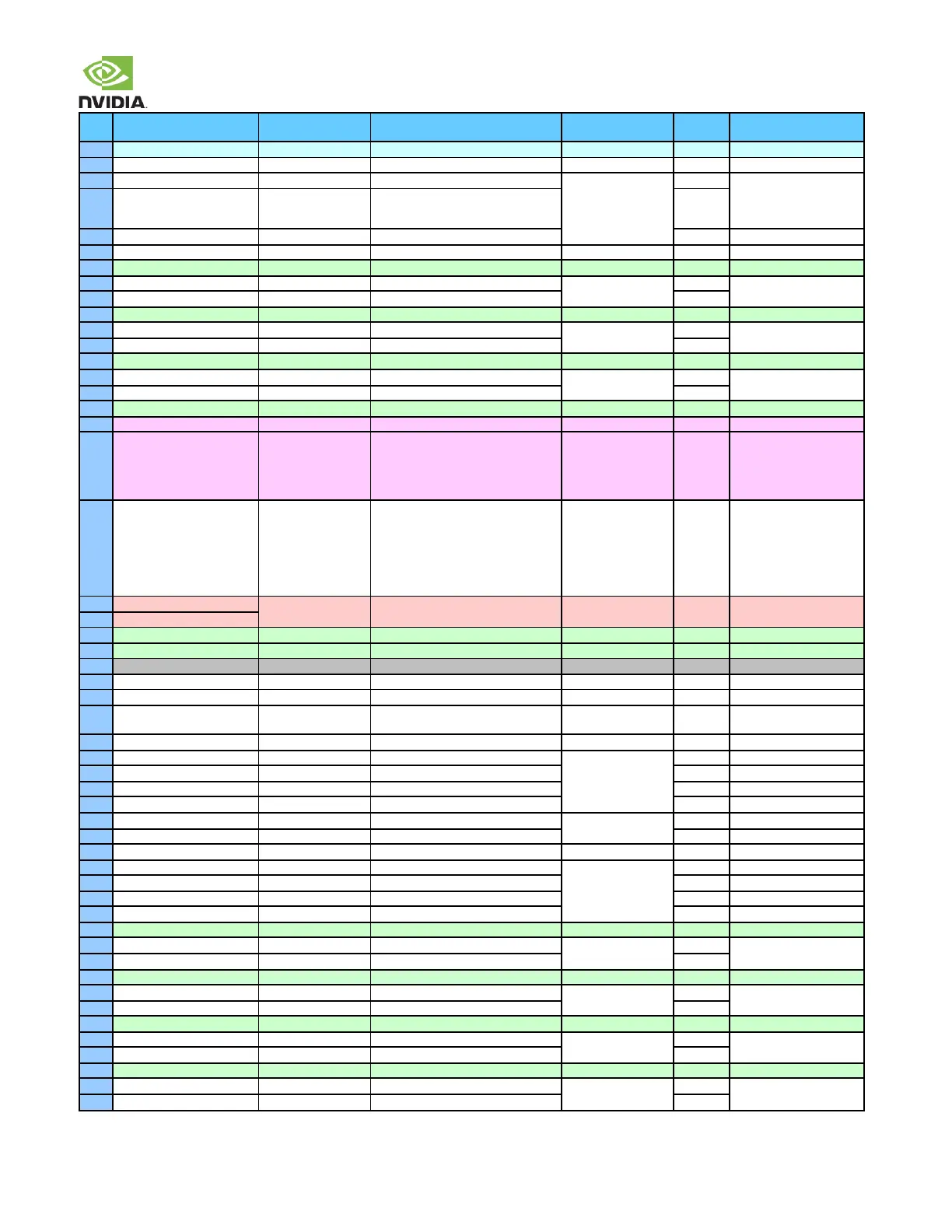

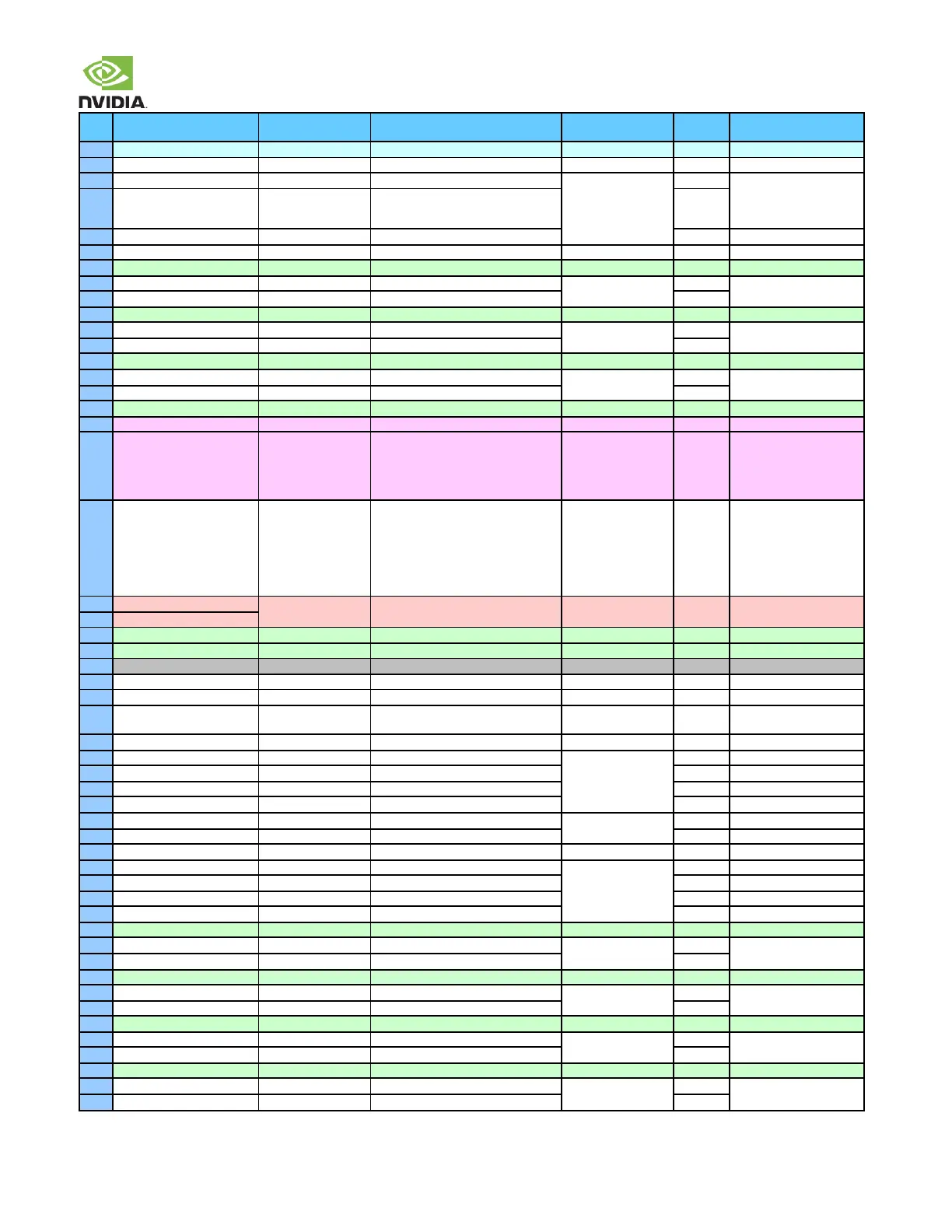

Usage on the Carrier

Board

Display Port 0 Aux or HDMI DDC SDA

AC-Coupled on Carrier

Board (eDP/DP) or Open-

Drain, 1.8V (3.3V tolerant -

DDC/I2C)

Display Port 0 Aux+ or HDMI DDC SCL

Display Port 0 Hot Plug Detect

PCIe 1 Reference Clock+ (PCIe IF #2)

PCIe 1 Reference Clock (PCIe IF #2)

Power button & SC7 wake interrupt

Module power configuration

identification. Tied to GND on Jetson

TX2i. Floating on Jetson TX2.

Determines the power-on mechanism

used to support both Jetson TX2 & TX2i.

Module power

configuration ID

Power Button. Used to initiate a system

power-on. Connected to PMIC EN0

-up to

VDD_5V0_SYS. Also connected to Tegra

POWER_ON pin through Diode with

-up to VDD_1V8_AP near

Tegra.

Main power Supplies PMIC & external

supplies

5.5V-19.6V (TX2)

9.0V-19.0V (TX2i)

Battery Over-current (& Thermal)

warning

Loading...

Loading...